Silicon on insulator: Difference between revisions

Citation bot (talk | contribs) m Alter: url, template type. Add: isbn, chapter-url. Removed or converted URL. Some additions/deletions were actually parameter name changes.| You can use this bot yourself. Report bugs here.| Activated by User:Nemo bis | via #UCB_webform |

|||

| (44 intermediate revisions by 32 users not shown) | |||

| Line 1: | Line 1: | ||

{{short description|Technology in semiconductor manufacturing}} |

|||

{{Hatnote|For silicon on insulator optical devices, see [[silicon photonics]].}} |

{{Hatnote|For silicon on insulator optical devices, see [[silicon photonics]].}} |

||

In [[semiconductor manufacturing]], '''silicon on insulator''' ('''SOI''') technology is fabrication of [[silicon]] |

In [[semiconductor manufacturing]], '''silicon on insulator''' ('''SOI''') technology is fabrication of [[silicon]] semiconductor devices in a layered silicon–insulator–silicon [[substrate (materials science)|substrate]], to reduce [[parasitic capacitance]] within the device, thereby improving performance.<ref name="celler">{{cite journal |last1=Celler |first1=G. K. |last2=Cristoloveanu |first2=S. |title=Frontiers of silicon-on-insulator |journal=[[Journal of Applied Physics]] |volume=93 |issue=9 |page=4955 |year=2003 |doi=10.1063/1.1558223 |bibcode=2003JAP....93.4955C }}</ref> SOI-based devices differ from conventional silicon-built devices in that the silicon junction is above an [[electrical insulator]], typically [[silicon dioxide]] or [[sapphire]] (these types of devices are called [[silicon on sapphire]], or SOS). The choice of insulator depends largely on intended application, with sapphire being used for high-performance radio frequency (RF) and radiation-sensitive applications, and silicon dioxide for diminished short-channel effects in other microelectronics devices.<ref>{{cite book |title=SOI design: analog, memory and digital techniques |first1=Andrew |last1=Marshall |first2=Sreedhar |last2=Natarajan |year=2002 |publisher=Kluwer |isbn=0-7923-7640-4}}</ref> The insulating layer and topmost silicon layer also vary widely with application.<ref>{{cite book |title=Silicon-on-Insulator Technology: Materials to VLSI |first=Jean-Pierre |last=Colinge |publisher=Springer |year=1991 |isbn=978-0-7923-9150-0}}</ref> |

||

==Industry need== |

==Industry need== |

||

SOI technology is one of several manufacturing strategies to allow the continued miniaturization of [[microelectronic]] devices, colloquially referred to as "extending [[Moore's Law]]" (or "More Moore", abbreviated "MM"). Reported benefits of SOI relative to conventional silicon ( |

SOI technology is one of several manufacturing strategies to allow the continued miniaturization of [[microelectronic]] devices, colloquially referred to as "extending [[Moore's Law]]" (or "More Moore", abbreviated "MM"). Reported benefits of SOI relative to conventional silicon ([[bulk CMOS]]) processing include:<ref> |

||

{{cite web |first=Horacio |last=Mendez |title=Silicon-on-insulator — SOI technology and ecosystem — Emerging SOI applications |date=April 2009 |publisher=SOI Industry Consortium |url=http://www.soiconsortium.org/pdf/Consortium_9april09_final.pdf }}</ref> |

|||

* |

*Lower parasitic capacitance due to isolation from the [[bulk silicon]], which improves power consumption at matched performance |

||

* |

*Resistance to [[latchup]] due to complete isolation of the n- and p-well structures |

||

*Higher performance at equivalent [[IC power-supply pin|VDD]]. Can work at low |

*Higher performance at equivalent [[IC power-supply pin|VDD]]. Can work at low VDDs<ref>{{cite web |first=Narayan M. |last=Kodeti |title=Silicon On Insulator (SOI) Implementation |date=October 2010 |work=White Paper |publisher=Infotech |url=http://www.infotech-enterprises.com/fileadmin/infotech-enterprises.com/assets/downloads/White_Papers/Infotech_SOI_Paper_Oct_2010.pdf|archive-url=https://web.archive.org/web/20130418043957/http://www.infotech-enterprises.com/fileadmin/infotech-enterprises.com/assets/downloads/White_Papers/Infotech_SOI_Paper_Oct_2010.pdf |archive-date=2013-04-18 }}</ref> |

||

*Reduced temperature dependency due to no doping |

*Reduced temperature dependency due to no doping |

||

*Better yield due to high density, better wafer utilization |

*Better yield due to high density, better wafer utilization |

||

| Line 16: | Line 17: | ||

From a manufacturing perspective, SOI substrates are compatible with most conventional fabrication processes. In general, an SOI-based process may be implemented without special equipment or significant retooling of an existing factory. Among challenges unique to SOI are novel [[metrology]] requirements to account for the buried oxide layer and concerns about differential stress in the topmost silicon layer. The threshold voltage of the transistor depends on the history of operation and applied voltage to it, thus making modeling harder. |

From a manufacturing perspective, SOI substrates are compatible with most conventional fabrication processes. In general, an SOI-based process may be implemented without special equipment or significant retooling of an existing factory. Among challenges unique to SOI are novel [[metrology]] requirements to account for the buried oxide layer and concerns about differential stress in the topmost silicon layer. The threshold voltage of the transistor depends on the history of operation and applied voltage to it, thus making modeling harder. |

||

The primary barrier to SOI implementation is the drastic increase in substrate cost, which contributes an estimated 10–15% increase to total manufacturing costs.<ref>{{cite web|url=https://www.cnet.com/news/ibm-touts-chipmaking-technology/|title=IBM touts chipmaking technology |

The primary barrier to SOI implementation is the drastic increase in substrate cost, which contributes an estimated 10–15% increase to total manufacturing costs.<ref>{{cite web|url=https://www.cnet.com/news/ibm-touts-chipmaking-technology/|title=IBM touts chipmaking technology|date=29 March 2001|website=cnet.com|access-date=22 April 2018}}</ref>{{additional citation needed|date=June 2018}} FD-SOI (Fully Depleted Silicon On Insulator) has been seen as a potential low cost alternative to FinFETs.<ref>{{cite web | url=https://www.eetimes.com/samsung-gf-ramp-fd-soi/ | title=Samsung, GF Ramp FD-SOI | date=27 April 2018 }}</ref> |

||

==SOI transistors== |

==SOI transistors== |

||

{{MOS|section|date=August 2023}} |

|||

An SOI MOSFET is a [[ |

An SOI MOSFET is a [[metal–oxide–semiconductor field-effect transistor]] (MOSFET) device in which a [[semiconductor]] layer such as silicon or [[germanium]] is formed on an insulator layer which may be a buried oxide (BOX) layer formed in a semiconductor substrate.<ref>{{cite patent |first= |last= |title=SOI wafers with 30-100 Ang. Buried OX created by wafer bonding using 30-100 Ang. thin oxide as bonding layer |country=US |number=6835633 |url=}}</ref><ref>{{cite patent |first= |last= |title=Ultra-thin body super-steep retrograde well (SSRW) FET devices |country=US |number=7002214 |url=}}</ref><ref>{{cite journal |author=Yang-Kyu Choi |last2=Asano |first2=K. |last3=Lindert |first3=N. |last4=Subramanian |first4=V. |author5=Tsu-Jae King |last6=Bokor |first6=J. |author7=Chenming Hu |title=Ultrathin-body SOI MOSFET for deep-sub-tenth micron era |journal=IEEE Electron Device Letters |volume=21 |issue=5 |pages=254–5 |date=May 2000 |doi=10.1109/IEDM.1999.824298 |s2cid=43561939 |url=http://www-device.eecs.berkeley.edu/~viveks/Papers/254EDL21.pdf}}</ref> SOI MOSFET devices are adapted for use by the computer industry.{{Citation needed|date=October 2008}} The buried oxide layer can be used in [[static random-access memory|SRAM]] designs.<ref>{{cite patent |first= |last= |title=Vertical MOSFET SRAM cell |country=US |number=7138685 |url=}} describes SOI buried oxide (BOX) structures and methods for implementing enhanced SOI BOX structures</ref> There are two types of SOI devices: PDSOI (partially depleted SOI) and FDSOI (fully depleted SOI) MOSFETs. For an n-type PDSOI MOSFET the sandwiched n-type film between the gate oxide (GOX) and buried oxide (BOX) is large, so the depletion region can't cover the whole n region. So to some extent PDSOI behaves like [[bulk MOSFET]]. Obviously there are some advantages over the bulk MOSFETs. The film is very thin in FDSOI devices so that the depletion region covers the whole channel region. In FDSOI the front gate (GOX) supports fewer depletion charges than the bulk so an increase in inversion charges occurs resulting in higher switching speeds. The limitation of the depletion charge by the BOX induces a suppression of the depletion capacitance and therefore a substantial reduction of the subthreshold swing allowing FD SOI MOSFETs to work at lower gate bias resulting in lower power operation. The [[Subthreshold slope|subthreshold swing]] can reach the minimum theoretical value for MOSFET at 300K, which is 60mV/decade. This ideal value was first demonstrated using numerical simulation.<ref>{{cite thesis |first=F. |last=Balestra |title=Characterization and Simulation of SOI MOSFETs with Back Potential Control |date=1985 |type=PhD |publisher=INP-Grenoble |url=}}</ref><ref>{{cite book |first=F. |last=Balestra |chapter=1.5 Challenges to Ultralow-Power Semiconductor Device Operation |title=Future Trends in Microelectronics—Journey into the unknown |editor-first=S. |editor-last=Lury |editor2-first=J. |editor2-last=Xu |editor3-first=A. |editor3-last=Zaslavsky |publisher=Wiley |date=2016 |doi=10.1002/9781119069225.ch1-5 |isbn=978-1-119-06922-5 |chapter-url={{GBurl|FPnoDAAAQBAJ|p=69}} |pages=69–81}}</ref> Other drawbacks in bulk MOSFETs, like threshold voltage roll off, etc. are reduced in FDSOI since the source and drain electric fields can't interfere due to the BOX. The main problem in PDSOI is the "[[floating body effect]] (FBE)" since the film is not connected to any of the supplies.{{Citation needed|date=June 2018}} |

||

==Manufacture of SOI wafers== |

==Manufacture of SOI wafers== |

||

[[File:SIMOX processing schematic.svg|thumb|300px|SIMOX process]] |

[[File:SIMOX processing schematic.svg|thumb|300px|SIMOX process]] |

||

[[File:Smart Cut SOI Wafer Manufacturing Schema.svg|thumb|300px|Smart Cut process]] |

[[File:Smart Cut SOI Wafer Manufacturing Schema.svg|thumb|300px|Smart Cut process]] |

||

SiO |

{{chem|SiO|2}}-based SOI wafers can be produced by several methods: |

||

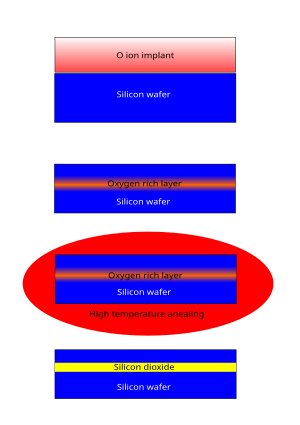

*''[[SIMOX]]'' - '''S'''eparation by '''IM'''plantation of '''OX'''ygen – uses an oxygen [[ion implantation|ion beam implantation]] process followed by high temperature annealing to create a buried SiO |

*''[[SIMOX]]'' - '''S'''eparation by '''IM'''plantation of '''OX'''ygen – uses an oxygen [[ion implantation|ion beam implantation]] process followed by high temperature annealing to create a buried {{chem|SiO|2}} layer.<ref>{{cite patent |inventor=Atsushi Ogura |title=Method of fabricating SOI substrate |country=US |number=5888297 |url= |gdate=1999-03-30}}</ref><ref>{{cite patent |inventor=Hiroshi Fujioka |title=Method of manufacturing semiconductor on insulator |country=US |number=5061642 |url= |gdate=1991-10-29}}</ref> |

||

*[[Wafer bonding]]<ref> |

*[[Wafer bonding]]<ref>{{cite book |first1=Q.-Y. |last1=Tong |first2=U. |last2=Gösele |title=SemiConductor Wafer Bonding: Science and Technology |publisher=Wiley |date=1998 |isbn=978-0-471-57481-1 |pages= |url=}}</ref><ref>{{cite patent |inventor-first=George |inventor-last=Bajor |invent2=et al. |title=Using a rapid thermal process for manufacturing a wafer bonded soi semiconductor |country=US |number=4771016 |url= |gdate=1988-09-13}}</ref> – the insulating layer is formed by directly bonding oxidized silicon with a second substrate. The majority of the second substrate is subsequently removed, the remnants forming the topmost Si layer. |

||

**One prominent example of a wafer bonding process is the ''[[Smart Cut]]'' method developed by the French firm [[Soitec]] which uses ion implantation followed by controlled exfoliation to determine the thickness of the uppermost silicon layer. |

**One prominent example of a wafer bonding process is the ''[[Smart Cut]]'' method developed by the French firm [[Soitec]] which uses ion implantation followed by controlled exfoliation to determine the thickness of the uppermost silicon layer. |

||

**''NanoCleave'' is a technology developed by Silicon Genesis Corporation that separates the silicon via stress at the interface of silicon and [[silicon-germanium]] alloy.<ref>{{cite web|url=http://www.sigen.com/|title=SIGEN.COM |

**''NanoCleave'' is a technology developed by Silicon Genesis Corporation that separates the silicon via stress at the interface of silicon and [[silicon-germanium]] alloy.<ref>{{cite web|url=http://www.sigen.com/|title=SIGEN.COM|website=www.sigen.com|access-date=22 April 2018}}</ref> |

||

**''ELTRAN'' is a technology developed by Canon which is based on porous silicon and water cut.<ref> |

**''ELTRAN'' is a technology developed by Canon which is based on porous silicon and water cut.<ref>{{cite web |last1=Yonehara |first1=T |last2=Sakaguchi |first2=K.|url=http://www.jsapi.jsap.or.jp/Pdf/Number04/CuttingEdge2.pdf |title=ELTRAN® Novel SOI Wafer Technology |work=Cutting Edge 2 |publisher=Canon}}</ref> |

||

*Seed methods<ref>{{ |

*Seed methods<ref>{{cite patent |country=US |number=5417180}}</ref> - wherein the topmost Si layer is grown directly on the insulator. Seed methods require some sort of template for homoepitaxy, which may be achieved by chemical treatment of the insulator, an appropriately oriented crystalline insulator, or vias through the insulator from the underlying substrate. |

||

An exhaustive review of these various manufacturing processes may be found in reference<ref name="celler"/> |

An exhaustive review of these various manufacturing processes may be found in reference<ref name="celler"/> |

||

== |

== Use in the microelectronics industry == |

||

| ⚫ | [[IBM]] began to use SOI in the high-end [[RS64#RS64-IV|RS64-IV]] "Istar" PowerPC-AS microprocessor in 2000. Other examples of microprocessors built on SOI technology include [[AMD]]'s 130 nm, 90 nm, 65 nm, 45 nm and 32 nm single, dual, quad, six and eight core processors since 2001.<ref>{{cite web |last=Vries |first=Hans de |date= |title=Chip Architect: Intel and Motorola/AMD's 130 nm processes to be revealed. |url=http://chip-architect.com/news/2000_11_07_process_130_nm.html |access-date=22 April 2018 |website=chip-architect.com}}</ref> [[Freescale]] adopted SOI in their [[PowerPC]] 7455 CPU in late 2001, currently{{when|date=April 2018}} Freescale is shipping SOI products in 180 nm, 130 nm, 90 nm and 45 nm lines.<ref>{{cite web |author= |date= |title=NXP Semiconductors - Automotive, Security, IoT |url=http://www.freescale.com/webapp/sps/site/overview.jsp?nodeId=0121000303#soi |access-date=22 April 2018 |website=www.freescale.com}}</ref> The 90 nm [[PowerPC]]- and [[Power ISA]]-based processors used in the [[Xbox 360]], [[PlayStation 3]], and [[Wii]] use SOI technology as well. Competitive offerings from [[Intel]] however continue{{when|date=April 2018}} to use conventional [[bulk CMOS]] technology for each process node, instead focusing on other venues such as [[HKMG]] and [[tri-gate transistor]]s to improve transistor performance. In January 2005, Intel researchers reported on an experimental single-chip silicon rib waveguide Raman laser built using SOI.<ref name="Intel 20052">{{cite journal |last1=Rong |first1=Haisheng |last2=Liu |first2=Ansheng |last3=Jones |first3=Richard |last4=Cohen |first4=Oded |last5=Hak |first5=Dani |last6=Nicolaescu |first6=Remus |last7=Fang |first7=Alexander |last8=Paniccia |first8=Mario |date=January 2005 |title=An all-silicon Raman laser |url=http://www.ece.ucsb.edu/uoeg/publications/papers/Rong05nature.pdf |journal=Nature |volume=433 |issue=7042 |pages=292–4 |doi=10.1038/nature03723|pmid=15931210 |s2cid=4423069 }}</ref> |

||

===Research=== |

|||

The silicon-on-insulator concept dates back to 1964, when it was proposed by C.W. Miller and P.H. Robinson.<ref>{{cite book |last1=Colinge |first1=Jean-Pierre |chapter=Multiplate-Gate Silicon-On-Insulator MOS Transistors |title=Microelectronics Technology and Devices, SBMICRO 2003: Proceedings of the Eighteenth International Symposium |date=2003 |publisher=[[The Electrochemical Society]] |isbn=9781566773898 |pages=2–17 |chapter-url=https://books.google.com/books?id=ibsOv36zIV0C&pg=PA2}}</ref> In 1979, a [[Texas Instruments]] research team including A.F. Tasch, T.C. Holloway and Kai Fong Lee [[semiconductor device fabrication|fabricated]] a silicon-on-insulator [[MOSFET]] (metal-oxide-semiconductor field-effect transistor).<ref>{{cite journal |last1=Tasch |first1=A. F. |last2=Holloway |first2=T. C. |last3=Lee |first3=K. F. |last4=Gibbons |first4=J. F. |title=Silicon-on-insulator m.o.s.f.e.t.s fabricated on laser-annealed polysilicon on SiO2 |journal=Electronics Letters |date=1979 |volume=15 |issue=14 |pages=435–437 |doi=10.1049/el:19790312}}</ref> In 1983, a [[Fujitsu]] research team led by S. Kawamura fabricated a [[three-dimensional integrated circuit]] with SOI [[CMOS]] (complementary metal-oxide-semiconductor) structure.<ref>{{cite journal |last1=Kawamura |first1=S. |last2=Sasaki |first2=N. |last3=Iwai |first3=T. |last4=Mukai |first4=R. |last5=Nakano |first5=M. |last6=Takagi |first6=M. |title=3-Dimensional SOI/CMOS IC's fabricated by beam recrystallization |journal=1983 International Electron Devices Meeting |date=December 1983 |pages=364–367 |doi=10.1109/IEDM.1983.190517}}</ref> In 1984, the same Fujitsu research team fabricated a 3D [[gate array]] with vertically-stacked dual SOI/CMOS structure using beam recrystallization.<ref>{{cite journal |last1=Kawamura |first1=S. |last2=Sasaki |first2=Nobuo |last3=Iwai |first3=T. |last4=Mukai |first4=R. |last5=Nakano |first5=M. |last6=Takagi |first6=M. |title=3-Dimensional Gate Array with Vertically Stacked Dual SOI/CMOS Structure Fabricated by Beam Recrystallization |journal=1984 Symposium on VLSI Technology. Digest of Technical Papers |date=1984 |pages=44–45 |url=https://ieeexplore.ieee.org/document/4480691}}</ref> The same year, [[Electrotechnical Laboratory]] researchers Toshihiro Sekigawa and Yutaka Hayashi fabricated a [[Multigate device|double-gate MOSFET]], demonstrating that [[short-channel effect]]s can be significantly reduced by sandwiching a fully depleted SOI device between two gate electrodes connected together.<ref name="Colinge">{{cite book |last1=Colinge |first1=Jean-Pierre |title=FinFETs and Other Multi-Gate Transistors |date=2008 |publisher=Springer Science & Business Media |isbn=9780387717517 |page=11 |url=https://books.google.com/books?id=t1ojkCdTGEEC&pg=PA11}}</ref><ref>{{cite journal |last1=Sekigawa |first1=Toshihiro |last2=Hayashi |first2=Yutaka |title=Calculated threshold-voltage characteristics of an XMOS transistor having an additional bottom gate |journal=Solid-State Electronics |date=1 August 1984 |volume=27 |issue=8 |pages=827–828 |doi=10.1016/0038-1101(84)90036-4 |issn=0038-1101}}</ref> In 1986, Jean-Pierre Colinge at [[HP Labs]] fabricated SOI [[NMOS logic|NMOS]] devices using [[90 nm]] thin [[silicon]] films.<ref>{{cite journal |last1=Colinge |first1=Jean-Pierre |title=Subthreshold slope of thin-film SOI MOSFET's |journal=IEEE Electron Device Letters |date=1986 |volume=7 |issue=4 |pages=244–246 |doi=10.1109/EDL.1986.26359}}</ref> |

|||

| ⚫ | As for the traditional foundries, in July 2006 [[TSMC]] claimed no customer wanted SOI,<ref>{{cite web |author= |date= |title=TSMC has no customer demand for SOI technology |publisher=Fabtech: The online information source for semiconductor professionals |url=http://www.fabtech.org/content/view/1698/74/ |archive-url=https://web.archive.org/web/20070928162940/http://www.fabtech.org/content/view/1698/74/ |archive-date=28 September 2007 |access-date=22 April 2018 }}</ref> but [[Chartered Semiconductor]] devoted a whole fab to SOI.<ref>[http://www.charteredsemi.com/media/corp/2006n/20060420_IBM_SOI.asp Chartered expands foundry market access to IBM's 90nm SOI technology]</ref> |

||

In 1989, [[Ghavam G. Shahidi]] initiated the SOI Research Program at the [[IBM Thomas J Watson Research Center]].<ref name="IEEE-Shahidi">{{cite web |title=Ghavam G. Shahidi |url=https://ieeexplore.ieee.org/author/37264864000 |website=[[IEEE Xplore]] |publisher=[[Institute of Electrical and Electronics Engineers]] |accessdate=16 September 2019}}</ref> He was the chief architect of SOI technology at [[IBM Microelectronics]], where he made fundamental contributions, from materials research to the development of the first commercially viable devices, with the support of his boss [[Bijan Davari]].<ref name="eetimes">{{Cite web|url=http://www.eetimes.com/story/OEG20010529S0126|title=SOI scientist counted among latest IBM fellows|website=[[EE Times]]|date=30 May 2001}}</ref> Shahidi was a key figure in making SOI CMOS technology a manufacturable reality. In the early 1990s, he demonstrated a novel technique of combining silicon [[epitaxial]] overgrowth and chemical mechanical polishing to prepare device-quality SOI material for fabricating devices and simple circuits, which led to [[IBM]] expanding its research program to include SOI substrates. He was also the first to demonstrate the power-delay advantage of SOI CMOS technology over traditional bulk CMOS in [[microprocessor]] applications. He overcame barriers preventing the [[semiconductor industry]]'s adoption of SOI, and was instrumental in driving SOI substrate development to the quality and cost levels suitable for mass-production.<ref name="ethw">{{cite web |title=Ghavam Shahidi |url=https://ethw.org/Ghavam_Shahidi |website=Engineering and Technology History |publisher=[[Institute of Electrical and Electronics Engineers]] |accessdate=16 September 2019}}</ref> |

|||

| ⚫ | |||

In 1994, an IBM research team led by Shahidi, [[Bijan Davari]] and [[Robert H. Dennard]] fabricated the first [[nanoelectronics|sub-100 nanometer]] SOI CMOS devices.<ref>{{cite journal |last1=Shahidi |first1=Ghavam G. |author1-link=Ghavam Shahidi |last2=Davari |first2=Bijan |author2-link=Bijan Davari |last3=Dennard |first3=Robert H. |author3-link=Robert H. Dennard |last4=Anderson |first4=C. A. |last5=Chappell |first5=B. A. |last6=Chappell |first6=T. I. |last7=Comfort |first7=J. H. |last8=Franch |first8=R. L. |last9=McFarland |first9=P. A. |last10=Neely |first10=J. S. |last11=Ning |first11=T. H. |last12=Polcari |first12=M. R. |last13=Warnock |first13=J. D. |display-authors=5 |title=A room temperature 0.1 µm CMOS on SOI |journal=IEEE Transactions on Electron Devices |date=December 1994 |volume=41 |issue=12 |pages=2405–2412 |doi=10.1109/16.337456}}</ref><ref>{{cite journal |last1=Critchlow |first1=D. L. |title=Recollections on MOSFET Scaling |journal=IEEE Solid-State Circuits Society Newsletter |date=2007 |volume=12 |issue=1 |pages=19–22 |doi=10.1109/N-SSC.2007.4785536 }}</ref> In 1998, a team of [[Hitachi]], [[TSMC]] and [[UC Berkeley]] researchers demonstrated the [[FinFET]] (fin [[field-effect transistor]]),<ref name="Liu">{{cite web |last1=Tsu‐Jae King |first1=Liu |authorlink1=Tsu-Jae King Liu |title=FinFET: History, Fundamentals and Future |url=https://people.eecs.berkeley.edu/~tking/presentations/KingLiu_2012VLSI-Tshortcourse |website=[[University of California, Berkeley]] |publisher=Symposium on VLSI Technology Short Course |date=June 11, 2012 |accessdate=9 July 2019}}</ref> which is a non-planar, double-gate MOSFET built on an SOI substrate.<ref>{{cite journal|first1=Digh|last1=Hisamoto|first2=Chenming|last2=Hu|authorlink2=Chenming Hu|first3=Xuejue|last3=Huang|first4=Wen-Chin |last4=Lee|first5=C.|last5=Kuo|first6=Leland|last6=Chang|first7=J.|last7=Kedzierski|first8=E.|last8=Anderson|first9=H.|last9=Takeuchi|first10=Yang-Kyu |last10=Choi|first11=K.|last11=Asano|first12=V.|last12=Subramanian|first13=Tsu-Jae |last13=King|first14=J.|last14=Bokor |display-authors=5 |title=Sub-50 nm P-channel FinFET |journal=IEEE Transactions on Electron Devices |date=May 2001 |volume=48 |issue=5 |pages=880–886 |doi=10.1109/16.918235|url=https://people.eecs.berkeley.edu/~hu/PUBLICATIONS/PAPERS/717.pdf}}</ref> In early 2001, Shahidi used SOI to developed a low-power [[RF CMOS]] device, resulting in increased radio frequency, at IBM.<ref name="eetimes"/> |

|||

| ⚫ | In 1990, [[Peregrine Semiconductor]] began development of an SOI process technology utilizing a standard 0.5 μm CMOS node and an enhanced sapphire substrate. Its patented [[silicon on sapphire]] (SOS) process is widely used in high-performance RF applications. The intrinsic benefits of the insulating sapphire substrate allow for high isolation, high linearity and electro-static discharge (ESD) tolerance. Multiple other companies have also applied SOI technology to successful RF applications in smartphones and cellular radios.<ref>{{cite news |title=Handset RFFEs: ''MMPAs, Envelope Tracking, Antenna Tuning, FEMs, and MIMO'' |first=Joe |last=Madden |url=http://mobile-experts.net/manuals/mexp-rffe-12%20toc.pdf |archive-url=https://web.archive.org/web/20160304044306/http://mobile-experts.net/manuals/mexp-rffe-12%20toc.pdf |archive-date=4 March 2016 |publisher= Mobile Experts |access-date=2 May 2012 }}</ref>{{additional citation needed|date=June 2018}} |

||

| ⚫ | |||

===Commercialization=== |

|||

| ⚫ | SOI wafers are widely used in [[silicon photonics]].<ref>{{cite book|url=https://books.google.com/books?id=6lsVVvFCBeAC&q=SOI+Wafers+in+Photonics&pg=PA111|title=Silicon Photonics: An Introduction|first1=Graham T.|last1=Reed|first2=Andrew P.|last2=Knights|date=5 March 2004|publisher=Wiley|access-date=22 April 2018|via=Google Books|isbn=978-0-470-87034-1}}</ref> The crystalline silicon layer on insulator can be used to fabricate optical waveguides and other optical devices, either passive or active (e.g. through suitable implantations). The buried insulator enables propagation of infrared light in the silicon layer on the basis of total internal reflection. The top surface of the waveguides can be either left uncovered and exposed to air (e.g. for sensing applications), or covered with a cladding, typically made of silica<ref>{{cite web |last1=Rigny |first1=Arnaud |title=Silicon-on-Insulator Substrates: The Basis of Silicon Photonics |url=https://www.photonics.com/Articles/Silicon-on-Insulator_Substrates_The_Basis_of/a63021 |website=Photonics.com |access-date=7 May 2023}}</ref> |

||

Shahidi's research at IBM led to the first commercial use of SOI in mainstream CMOS technology.<ref name="IEEE-Shahidi"/> SOI was first commercialized in 1995, when Shahidi's work on SOI convinced John Kelly, who ran IBM's server division, to adopt SOI in the [[AS/400]] line of server products, which used [[250 nanometer|220 nm]] CMOS with copper metallization SOI devices.<ref name="eetimes"/> IBM began to use SOI in the high-end [[RS64#RS64-IV|RS64-IV]] "Istar" PowerPC-AS [[microprocessor]] in 2000. Other examples of microprocessors built on SOI technology include [[AMD]]'s 130 nm, 90 nm, 65 nm, 45 nm and 32 nm single, dual, quad, six and eight core processors since 2001.<ref>{{cite web|url=http://chip-architect.com/news/2000_11_07_process_130_nm.html|title=Chip Architect: Intel and Motorola/AMD's 130 nm processes to be revealed.|first=Hans de|last=Vries|date=|website=chip-architect.com|accessdate=22 April 2018}}</ref> |

|||

== Disadvantages == |

|||

| ⚫ | |||

The major disadvantage of SOI technology when compared to conventional semiconductor industry is increased cost of manufacturing.<ref name=":0">{{Cite web|last=McLellan|first=Paul|title=Silicon on Insulator (SOI)|url=https://semiwiki.com/semiconductor-services/1470-silicon-on-insulator-soi/|access-date=2021-03-07|website=Semiwiki|language=en-US}}</ref> As of 2012 only IBM and AMD used SOI as basis for high-performance processors and the other manufacturers (Intel, TSMC, Global Foundries etc.) used conventional silicon wafers to build their [[CMOS]] chips.<ref name=":0" /> |

|||

== SOI market == |

|||

| ⚫ | As for the traditional foundries, |

||

As of 2020 the market utilizing the SOI process was projected to grow up by ~15% for the next 5 years according to Market Research Future group.<ref>{{Cite press release|last=Future|first=Market Research|date=2021-02-17|title=Silicon on Insulator (SoI) Market is Anticipated to Surpass USD 2.40 Billion By 2026 {{!}} APAC Region to Remain Forerunner in Global Silicon on Insulator Industry|url=http://www.globenewswire.com/news-release/2021/02/17/2176707/0/en/Silicon-on-Insulator-SoI-Market-is-Anticipated-to-Surpass-USD-2-40-Billion-By-2026-APAC-Region-to-Remain-Forerunner-in-Global-Silicon-on-Insulator-Industry.html|access-date=2021-03-07|website=GlobeNewswire News Room}}</ref> |

|||

| ⚫ | |||

| ⚫ | In 1990, [[Peregrine Semiconductor]] began development of an SOI process technology utilizing a standard 0.5 μm CMOS node and an enhanced sapphire substrate. Its patented [[silicon on sapphire]] (SOS) process is widely used in high-performance RF applications. The intrinsic benefits of the insulating sapphire substrate allow for high isolation, high linearity and electro-static discharge (ESD) tolerance. Multiple other companies have also applied SOI technology to successful RF applications in smartphones and cellular radios.<ref>{{cite news |title=Handset RFFEs: ''MMPAs, Envelope Tracking, Antenna Tuning, FEMs, and MIMO'' |first=Joe |last=Madden |url=http://mobile-experts.net/manuals/mexp-rffe-12%20toc.pdf |archive-url=https://web.archive.org/web/20160304044306/http://mobile-experts.net/manuals/mexp-rffe-12%20toc.pdf |

||

| ⚫ | |||

| ⚫ | SOI wafers are widely used in [[silicon photonics]].<ref>{{cite book|url=https://books.google.com/?id=6lsVVvFCBeAC& |

||

==See also== |

==See also== |

||

| ⚫ | |||

*[[CMOS]] |

|||

*[[ |

* [[Strain engineering]] |

||

| ⚫ | |||

| ⚫ | |||

*[[ |

* [[Wafer bonding]] |

||

*[[Silicon on sapphire]] |

|||

*[[Strain engineering]] |

|||

| ⚫ | |||

*[[Wafer bonding]] |

|||

==References== |

==References== |

||

Latest revision as of 06:57, 30 September 2024

In semiconductor manufacturing, silicon on insulator (SOI) technology is fabrication of silicon semiconductor devices in a layered silicon–insulator–silicon substrate, to reduce parasitic capacitance within the device, thereby improving performance.[1] SOI-based devices differ from conventional silicon-built devices in that the silicon junction is above an electrical insulator, typically silicon dioxide or sapphire (these types of devices are called silicon on sapphire, or SOS). The choice of insulator depends largely on intended application, with sapphire being used for high-performance radio frequency (RF) and radiation-sensitive applications, and silicon dioxide for diminished short-channel effects in other microelectronics devices.[2] The insulating layer and topmost silicon layer also vary widely with application.[3]

Industry need

[edit]SOI technology is one of several manufacturing strategies to allow the continued miniaturization of microelectronic devices, colloquially referred to as "extending Moore's Law" (or "More Moore", abbreviated "MM"). Reported benefits of SOI relative to conventional silicon (bulk CMOS) processing include:[4]

- Lower parasitic capacitance due to isolation from the bulk silicon, which improves power consumption at matched performance

- Resistance to latchup due to complete isolation of the n- and p-well structures

- Higher performance at equivalent VDD. Can work at low VDDs[5]

- Reduced temperature dependency due to no doping

- Better yield due to high density, better wafer utilization

- Reduced antenna issues

- No body or well taps are needed

- Lower leakage currents due to isolation thus higher power efficiency

- Inherently radiation hardened (resistant to soft errors), reducing the need for redundancy

From a manufacturing perspective, SOI substrates are compatible with most conventional fabrication processes. In general, an SOI-based process may be implemented without special equipment or significant retooling of an existing factory. Among challenges unique to SOI are novel metrology requirements to account for the buried oxide layer and concerns about differential stress in the topmost silicon layer. The threshold voltage of the transistor depends on the history of operation and applied voltage to it, thus making modeling harder. The primary barrier to SOI implementation is the drastic increase in substrate cost, which contributes an estimated 10–15% increase to total manufacturing costs.[6][additional citation(s) needed] FD-SOI (Fully Depleted Silicon On Insulator) has been seen as a potential low cost alternative to FinFETs.[7]

SOI transistors

[edit]This section needs editing to comply with Wikipedia's Manual of Style. (August 2023) |

An SOI MOSFET is a metal–oxide–semiconductor field-effect transistor (MOSFET) device in which a semiconductor layer such as silicon or germanium is formed on an insulator layer which may be a buried oxide (BOX) layer formed in a semiconductor substrate.[8][9][10] SOI MOSFET devices are adapted for use by the computer industry.[citation needed] The buried oxide layer can be used in SRAM designs.[11] There are two types of SOI devices: PDSOI (partially depleted SOI) and FDSOI (fully depleted SOI) MOSFETs. For an n-type PDSOI MOSFET the sandwiched n-type film between the gate oxide (GOX) and buried oxide (BOX) is large, so the depletion region can't cover the whole n region. So to some extent PDSOI behaves like bulk MOSFET. Obviously there are some advantages over the bulk MOSFETs. The film is very thin in FDSOI devices so that the depletion region covers the whole channel region. In FDSOI the front gate (GOX) supports fewer depletion charges than the bulk so an increase in inversion charges occurs resulting in higher switching speeds. The limitation of the depletion charge by the BOX induces a suppression of the depletion capacitance and therefore a substantial reduction of the subthreshold swing allowing FD SOI MOSFETs to work at lower gate bias resulting in lower power operation. The subthreshold swing can reach the minimum theoretical value for MOSFET at 300K, which is 60mV/decade. This ideal value was first demonstrated using numerical simulation.[12][13] Other drawbacks in bulk MOSFETs, like threshold voltage roll off, etc. are reduced in FDSOI since the source and drain electric fields can't interfere due to the BOX. The main problem in PDSOI is the "floating body effect (FBE)" since the film is not connected to any of the supplies.[citation needed]

Manufacture of SOI wafers

[edit]

SiO

2-based SOI wafers can be produced by several methods:

- SIMOX - Separation by IMplantation of OXygen – uses an oxygen ion beam implantation process followed by high temperature annealing to create a buried SiO

2 layer.[14][15] - Wafer bonding[16][17] – the insulating layer is formed by directly bonding oxidized silicon with a second substrate. The majority of the second substrate is subsequently removed, the remnants forming the topmost Si layer.

- One prominent example of a wafer bonding process is the Smart Cut method developed by the French firm Soitec which uses ion implantation followed by controlled exfoliation to determine the thickness of the uppermost silicon layer.

- NanoCleave is a technology developed by Silicon Genesis Corporation that separates the silicon via stress at the interface of silicon and silicon-germanium alloy.[18]

- ELTRAN is a technology developed by Canon which is based on porous silicon and water cut.[19]

- Seed methods[20] - wherein the topmost Si layer is grown directly on the insulator. Seed methods require some sort of template for homoepitaxy, which may be achieved by chemical treatment of the insulator, an appropriately oriented crystalline insulator, or vias through the insulator from the underlying substrate.

An exhaustive review of these various manufacturing processes may be found in reference[1]

Use in the microelectronics industry

[edit]IBM began to use SOI in the high-end RS64-IV "Istar" PowerPC-AS microprocessor in 2000. Other examples of microprocessors built on SOI technology include AMD's 130 nm, 90 nm, 65 nm, 45 nm and 32 nm single, dual, quad, six and eight core processors since 2001.[21] Freescale adopted SOI in their PowerPC 7455 CPU in late 2001, currently[when?] Freescale is shipping SOI products in 180 nm, 130 nm, 90 nm and 45 nm lines.[22] The 90 nm PowerPC- and Power ISA-based processors used in the Xbox 360, PlayStation 3, and Wii use SOI technology as well. Competitive offerings from Intel however continue[when?] to use conventional bulk CMOS technology for each process node, instead focusing on other venues such as HKMG and tri-gate transistors to improve transistor performance. In January 2005, Intel researchers reported on an experimental single-chip silicon rib waveguide Raman laser built using SOI.[23]

As for the traditional foundries, in July 2006 TSMC claimed no customer wanted SOI,[24] but Chartered Semiconductor devoted a whole fab to SOI.[25]

Use in high-performance radio frequency (RF) applications

[edit]In 1990, Peregrine Semiconductor began development of an SOI process technology utilizing a standard 0.5 μm CMOS node and an enhanced sapphire substrate. Its patented silicon on sapphire (SOS) process is widely used in high-performance RF applications. The intrinsic benefits of the insulating sapphire substrate allow for high isolation, high linearity and electro-static discharge (ESD) tolerance. Multiple other companies have also applied SOI technology to successful RF applications in smartphones and cellular radios.[26][additional citation(s) needed]

Use in photonics

[edit]SOI wafers are widely used in silicon photonics.[27] The crystalline silicon layer on insulator can be used to fabricate optical waveguides and other optical devices, either passive or active (e.g. through suitable implantations). The buried insulator enables propagation of infrared light in the silicon layer on the basis of total internal reflection. The top surface of the waveguides can be either left uncovered and exposed to air (e.g. for sensing applications), or covered with a cladding, typically made of silica[28]

Disadvantages

[edit]The major disadvantage of SOI technology when compared to conventional semiconductor industry is increased cost of manufacturing.[29] As of 2012 only IBM and AMD used SOI as basis for high-performance processors and the other manufacturers (Intel, TSMC, Global Foundries etc.) used conventional silicon wafers to build their CMOS chips.[29]

SOI market

[edit]As of 2020 the market utilizing the SOI process was projected to grow up by ~15% for the next 5 years according to Market Research Future group.[30]

See also

[edit]- Intel TeraHertz - similar technology from Intel

- Strain engineering

- Wafer (electronics)

- Wafer bonding

References

[edit]- ^ a b Celler, G. K.; Cristoloveanu, S. (2003). "Frontiers of silicon-on-insulator". Journal of Applied Physics. 93 (9): 4955. Bibcode:2003JAP....93.4955C. doi:10.1063/1.1558223.

- ^ Marshall, Andrew; Natarajan, Sreedhar (2002). SOI design: analog, memory and digital techniques. Kluwer. ISBN 0-7923-7640-4.

- ^ Colinge, Jean-Pierre (1991). Silicon-on-Insulator Technology: Materials to VLSI. Springer. ISBN 978-0-7923-9150-0.

- ^ Mendez, Horacio (April 2009). "Silicon-on-insulator — SOI technology and ecosystem — Emerging SOI applications" (PDF). SOI Industry Consortium.

- ^ Kodeti, Narayan M. (October 2010). "Silicon On Insulator (SOI) Implementation" (PDF). White Paper. Infotech. Archived from the original (PDF) on 2013-04-18.

- ^ "IBM touts chipmaking technology". cnet.com. 29 March 2001. Retrieved 22 April 2018.

- ^ "Samsung, GF Ramp FD-SOI". 27 April 2018.

- ^ US 6835633, "SOI wafers with 30-100 Ang. Buried OX created by wafer bonding using 30-100 Ang. thin oxide as bonding layer"

- ^ US 7002214, "Ultra-thin body super-steep retrograde well (SSRW) FET devices"

- ^ Yang-Kyu Choi; Asano, K.; Lindert, N.; Subramanian, V.; Tsu-Jae King; Bokor, J.; Chenming Hu (May 2000). "Ultrathin-body SOI MOSFET for deep-sub-tenth micron era" (PDF). IEEE Electron Device Letters. 21 (5): 254–5. doi:10.1109/IEDM.1999.824298. S2CID 43561939.

- ^ US 7138685, "Vertical MOSFET SRAM cell" describes SOI buried oxide (BOX) structures and methods for implementing enhanced SOI BOX structures

- ^ Balestra, F. (1985). Characterization and Simulation of SOI MOSFETs with Back Potential Control (PhD). INP-Grenoble.

- ^ Balestra, F. (2016). "1.5 Challenges to Ultralow-Power Semiconductor Device Operation". In Lury, S.; Xu, J.; Zaslavsky, A. (eds.). Future Trends in Microelectronics—Journey into the unknown. Wiley. pp. 69–81. doi:10.1002/9781119069225.ch1-5. ISBN 978-1-119-06922-5.

- ^ US 5888297, Atsushi Ogura, "Method of fabricating SOI substrate", issued 1999-03-30

- ^ US 5061642, Hiroshi Fujioka, "Method of manufacturing semiconductor on insulator", issued 1991-10-29

- ^ Tong, Q.-Y.; Gösele, U. (1998). SemiConductor Wafer Bonding: Science and Technology. Wiley. ISBN 978-0-471-57481-1.

- ^ US 4771016, Bajor, George & et al., "Using a rapid thermal process for manufacturing a wafer bonded soi semiconductor", issued 1988-09-13

- ^ "SIGEN.COM". www.sigen.com. Retrieved 22 April 2018.

- ^ Yonehara, T; Sakaguchi, K. "ELTRAN® Novel SOI Wafer Technology" (PDF). Cutting Edge 2. Canon.

- ^ US 5417180

- ^ Vries, Hans de. "Chip Architect: Intel and Motorola/AMD's 130 nm processes to be revealed". chip-architect.com. Retrieved 22 April 2018.

- ^ "NXP Semiconductors - Automotive, Security, IoT". www.freescale.com. Retrieved 22 April 2018.

- ^ Rong, Haisheng; Liu, Ansheng; Jones, Richard; Cohen, Oded; Hak, Dani; Nicolaescu, Remus; Fang, Alexander; Paniccia, Mario (January 2005). "An all-silicon Raman laser" (PDF). Nature. 433 (7042): 292–4. doi:10.1038/nature03723. PMID 15931210. S2CID 4423069.

- ^ "TSMC has no customer demand for SOI technology". Fabtech: The online information source for semiconductor professionals. Archived from the original on 28 September 2007. Retrieved 22 April 2018.

- ^ Chartered expands foundry market access to IBM's 90nm SOI technology

- ^ Madden, Joe. "Handset RFFEs: MMPAs, Envelope Tracking, Antenna Tuning, FEMs, and MIMO" (PDF). Mobile Experts. Archived from the original (PDF) on 4 March 2016. Retrieved 2 May 2012.

- ^ Reed, Graham T.; Knights, Andrew P. (5 March 2004). Silicon Photonics: An Introduction. Wiley. ISBN 978-0-470-87034-1. Retrieved 22 April 2018 – via Google Books.

- ^ Rigny, Arnaud. "Silicon-on-Insulator Substrates: The Basis of Silicon Photonics". Photonics.com. Retrieved 7 May 2023.

- ^ a b McLellan, Paul. "Silicon on Insulator (SOI)". Semiwiki. Retrieved 2021-03-07.

- ^ Future, Market Research (2021-02-17). "Silicon on Insulator (SoI) Market is Anticipated to Surpass USD 2.40 Billion By 2026 | APAC Region to Remain Forerunner in Global Silicon on Insulator Industry". GlobeNewswire News Room (Press release). Retrieved 2021-03-07.

External links

[edit]- SOI Industry Consortium - a site with extensive information and education for SOI technology

- SOI IP portal - A search engine for SOI IP

- AMDboard - a site with extensive information regarding SOI technology

- Advanced Substrate News - a newsletter about the SOI industry, produced by Soitec

- MIGAS '04 - The 7th session of MIGAS International Summer School on Advanced Microelectronics, devoted to SOI technology and devices

- MIGAS '09 - 12th session of the International Summer School on Advanced Microelectronics: "Silicon on Insulator (SOI) Nanodevices"