Via (electronics): Difference between revisions

m In printed circuit boards: + article |

deleted warning |

||

| (11 intermediate revisions by 6 users not shown) | |||

| Line 1: | Line 1: | ||

{{Short description|Type of electrical connection}} |

{{Short description|Type of electrical connection}}{{About|A way of connecting PCBs|3=Via (disambiguation)}}{{Use dmy dates||date=February 2022|cs1-dates=y}} |

||

{{More footnotes needed|date=December 2017}} |

|||

{{Use dmy dates||date=February 2022|cs1-dates=y}} |

|||

{{Use list-defined references|date=February 2022}} |

{{Use list-defined references|date=February 2022}} |

||

{{Anchor|Castellated hole|DVIA|Stacked via|Staggered via|Via-in-pad|Padstack|Viastack}}<!-- parked anchors from redirects --> |

{{Anchor|Castellated hole|DVIA|Stacked via|Staggered via|Via-in-pad|Padstack|Viastack}}<!-- parked anchors from redirects --> |

||

| ⚫ | |||

A '''via''' (Latin, 'path' or 'way') is an [[electrical connection]] between two or more metal layers |

A '''via''' (Latin, 'path' or 'way') is an [[electrical connection]] between two or more metal layers of a [[printed circuit board]]s (PCB) or [[integrated circuit]]. Essentially a via is a small drilled hole that goes through two or more adjacent layers; the hole is plated with metal (often copper) that forms an electrical connection through the insulating layers. |

||

Vias are an important concern in PCB manufacturing.<ref name="Epiccolo"/> As vertical structures crossing multiple layers, they are specified differently from most of the design, which increases the chance for errors. They place the strictest demands on registration (how closely aligned different layers are). They are manufactured with different tooling from other features -- tooling that typically has looser tolerances. If either the hole or any layer is slightly out of place, the wrong electrical connections may be made; this may not be visible from the surface. After the hole is drilled, it must also be lined with conductive material, as opposed to simply leaving conductive material in place on copper layers. Even an initially good board may develop problems later because the via reacts to heat differently from the substrate around it. Vias also represent a discontinuity in the [[electrical impedance]], which can cause problems for [[signal integrity]]. |

|||

Vias are an important concern in PCB manufacturing.<ref name="Epiccolo"/> This is because the vias are drilled with certain tolerances and may be fabricated off their designated locations, so some allowance for errors in drill position must be made prior to manufacturing or else the manufacturing yield can decrease due to non-conforming boards (according to some reference standard) or even due to failing boards. In addition, regular through-hole vias are considered fragile structures as they are long and narrow; the manufacturer must ensure that the vias are plated properly throughout the barrel and this in turn causes several processing steps. |

|||

=={{anchor|Buried via|Blind via|Thermal via|Through via|Non-through via}} In printed circuit boards == |

=={{anchor|Buried via|Blind via|Thermal via|Through via|Non-through via}} In printed circuit boards == |

||

| ⚫ | |||

[[File:ViaCurrentCapacity.png|thumb|PCB via current capacity chart showing 1 mil plating via current capacity & resistance versus diameter on a 1.6 mm PCB.]] |

[[File:ViaCurrentCapacity.png|thumb|PCB via current capacity chart showing 1 mil plating via current capacity & resistance versus diameter on a 1.6 mm PCB.]] |

||

| Line 20: | Line 18: | ||

# Antipad — clearance hole between barrel and metal layer to which it is not connected |

# Antipad — clearance hole between barrel and metal layer to which it is not connected |

||

[[File:Raspberry pi pico oben (cropped).jpg|thumb|[[Raspberry Pi Pico]] with castellated holes]] |

|||

A via, sometimes called PTV or plated-through-via, should not be confused with a plated through hole (PTH). A via is used as an interconnection between copper layers on a PCB while the PTH is generally made larger than vias and is used as a plated hole for acceptance of component leads - such as non-SMT resistors, capacitors, and DIP package IC. PTH can also be used as holes for mechanical connection while vias may not. Another usage of PTH is known as a '''castellated hole''' where the PTH is aligned at the edge of the board so that it is cut in half when the board is milled out of the panel - the main usage is for allowing one PCB to be soldered to another in a stack - thus acting both as a fastener and also as a connector.<ref name="Castell"/> |

A via, sometimes called PTV or plated-through-via, should not be confused with a plated through hole (PTH). A via is used as an interconnection between copper layers on a PCB while the PTH is generally made larger than vias and is used as a plated hole for acceptance of component leads - such as non-SMT resistors, capacitors, and DIP package IC. PTH can also be used as holes for mechanical connection while vias may not. Another usage of PTH is known as a '''castellated hole''' where the PTH is aligned at the edge of the board so that it is cut in half when the board is milled out of the panel - the main usage is for allowing one PCB to be soldered to another in a stack - thus acting both as a fastener and also as a connector.<ref name="Castell"/> |

||

Three major kinds of vias are shown in right figure. The basic steps of making a PCB are: making the substrate material and stacking it in layers; through-drilling of plating the vias; and copper trace patterning using photolithography and etching. With this standard procedure, possible via configurations are limited to through-holes.{{efn|Through-holes per core. It is possible, though more expensive, to create blind or buried vias by using additional cores and lamination steps. It is also possible to backdrill and remove the plating from one side through to the desired layer, which leaves the physical hole as a through-hole, but creates the electrical equivalent of a blind via. If a PCB needs enough layers to justify blind and buried vias, it is probably also using small enough traces packed tightly enough to require (laser-drilled) microvias.}} Depth-controlled drilling techniques such as using lasers can allow for more varied via types. |

Three major kinds of vias are shown in right figure. The basic steps of making a PCB are: making the substrate material and stacking it in layers; through-drilling of plating the vias; and copper trace patterning using photolithography and etching. With this standard procedure, possible via configurations are limited to through-holes.{{efn|Through-holes per core. It is possible, though more expensive, to create blind or buried vias by using additional cores and lamination steps. It is also possible to backdrill and remove the plating from one side through to the desired layer, which leaves the physical hole as a through-hole, but creates the electrical equivalent of a blind via. If a PCB needs enough layers to justify blind and buried vias, it is probably also using small enough traces packed tightly enough to require (laser-drilled) microvias.}} Depth-controlled drilling techniques such as using lasers can allow for more varied via types. Laser drills can also be used for smaller and more precisely positioned holes than mechanical drills produce. PCB manufacturing typically starts with a so-called core, a basic double-sided PCB. Layers beyond the first two are stacked from this basic building block. If two more layers are consecutively stacked from bottom of core, you can have a 1-2 via, a 1-3 via and a [[through hole]]. Each type of via is made by drilling at each stacking stage. If one layer is stacked on top of the core and other is stacked from the bottom, the possible via configurations are 1-3, 2-3 and through hole. The user must gather information about the PCB manufacturer's allowed methods of stacking and possible vias. For cheaper boards, only through holes are made and antipad (or clearance) is placed on layers which are supposed not to be contacted to vias. |

||

== IPC 4761 == |

== IPC 4761 == |

||

{{Anchor|I|II|III|III-a|III-b|IV|IV-a|IV-b|V|VI|VI-a|VI-b|VII|Tented via|Covered annular ring|Plugged via|Filled via|Capped via|Covered via|Filled microvia|Blind microvia}}IPC 4761 defines the following via types: |

{{Anchor|I|II|III|III-a|III-b|IV|IV-a|IV-b|V|VI|VI-a|VI-b|VII|Tented via|Covered annular ring|Plugged via|Filled via|Capped via|Covered via|Filled microvia|Blind microvia}}IPC 4761 defines the following via types: |

||

* Type I: Tented via |

* Type I: Tented via |

||

* Type II: Tented & covered via |

* Type II: Tented & covered via |

||

* Type III-a: Plugged via, sealed with non-conductive material on one side |

* Type III-a: Plugged via, sealed with non-conductive material on one side |

||

* Type III-b: Plugged via, sealed with non-conductive material on both sides |

* Type III-b: Plugged via, sealed with non-conductive material on both sides |

||

* Type IV-a: Plugged & covered via, sealed with non-conductive material and covered with wet solder mask on one side |

* Type IV-a: Plugged & covered via, sealed with non-conductive material and covered with wet solder mask on one side |

||

* Type IV-b: Plugged & covered via, sealed with non-conductive material and covered with wet solder mask on both sides |

* Type IV-b: Plugged & covered via, sealed with non-conductive material and covered with wet solder mask on both sides |

||

* Type V: Filled via, filled with non-conductive paste |

* Type V: Filled via, filled with non-conductive paste |

||

| Line 46: | Line 44: | ||

== Gallery == |

== Gallery == |

||

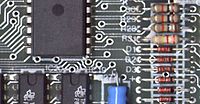

{{Gallery|width=200|File:Durchkontaktierung IMGP3005.jpg| Plated-through holes |

{{Gallery|width=200|File:Durchkontaktierung IMGP3005.jpg| Plated-through holes on a multilayer board (magnified) |

||

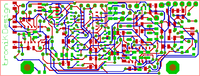

|File:Lp3b.png| Double layered plating in CAD. Vias makes [[Placement (EDA)|EDA placement]] possible.<br/> {{fontcolor|red|Bottom layer – Red}}<br/> {{fontcolor|blue|Top layer – Blue}} |

|File:Lp3b.png| Double layered plating in CAD. Vias makes [[Placement (EDA)|EDA placement]] possible.<br/> {{fontcolor|red|Bottom layer – Red}}<br/> {{fontcolor|blue|Top layer – Blue}} |

||

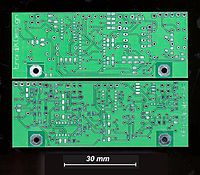

|File:dldklpcb.jpg| Plating of plated-through holes:<br/>Above – Top layer<br/>Down – Bottom layer |

|File:dldklpcb.jpg| Plating of plated-through holes:<br/>Above – Top layer<br/>Down – Bottom layer |

||

| Line 79: | Line 77: | ||

==Further reading== |

==Further reading== |

||

* {{cite web |title=Tips for PCB Vias Design |publisher=Quick-teck |type=Technical note |id=EN-00417 |date=2014 |url=http://www.quick-teck.co.uk/TechArticleDoc/19895134801360697091.pdf |access-date=2017-12-18}} |

* {{cite web |title=Tips for PCB Vias Design |publisher=Quick-teck |type=Technical note |id=EN-00417 |date=2014 |url=http://www.quick-teck.co.uk/TechArticleDoc/19895134801360697091.pdf |access-date=2017-12-18}} |

||

* {{cite web |title=Via Tenting - Overview of the variations |at=Printed Circuit Boards > Layout > Design Tip > Tenting |publisher=[[Würth Elektronik GmbH & Co. KG]] |website=[[WE Online]] |date=2014 |url=http://www.we-online.com/web/en/leiterplatten/layout/design_tipp/tenting/tenting_3.php |access-date=2017-12-18 |url-status=live |archive-url=https://web.archive.org/web/20171218141422/http://www.we-online.com/web/en/leiterplatten/layout/design_tipp/tenting/tenting_3.php |archive-date=2017-12-18}} |

* {{cite web |title=Via Tenting - Overview of the variations |at=Printed Circuit Boards > Layout > Design Tip > Tenting |publisher=[[Würth Elektronik GmbH & Co. KG]] |website=[[WE Online]] |date=2014 |url=http://www.we-online.com/web/en/leiterplatten/layout/design_tipp/tenting/tenting_3.php |access-date=2017-12-18 |url-status=live |archive-url=https://web.archive.org/web/20171218141422/http://www.we-online.com/web/en/leiterplatten/layout/design_tipp/tenting/tenting_3.php |archive-date=2017-12-18}} |

||

* {{cite web |title=Via Plugging - Overview of the variations |at=Printed Circuit Boards > Layout > Design Tip > Plugging |publisher=[[Würth Elektronik GmbH & Co. KG]] |website=[[WE Online]] |date=2014 |url=http://www.we-online.com/web/en/leiterplatten/layout/design_tipp/plugging/plugging_1.php |access-date=2017-12-18 |url-status=live |archive-url=https://web.archive.org/web/20171218141631/http://www.we-online.com/web/en/leiterplatten/layout/design_tipp/plugging/plugging_1.php |archive-date=2017-12-18}} |

* {{cite web |title=Via Plugging - Overview of the variations |at=Printed Circuit Boards > Layout > Design Tip > Plugging |publisher=[[Würth Elektronik GmbH & Co. KG]] |website=[[WE Online]] |date=2014 |url=http://www.we-online.com/web/en/leiterplatten/layout/design_tipp/plugging/plugging_1.php |access-date=2017-12-18 |url-status=live |archive-url=https://web.archive.org/web/20171218141631/http://www.we-online.com/web/en/leiterplatten/layout/design_tipp/plugging/plugging_1.php |archive-date=2017-12-18}} |

||

* {{cite web |title=Via Filling - Overview of the variations |at=Printed Circuit Boards > Layout > Design Tip > Filling |publisher=[[Würth Elektronik GmbH & Co. KG]] |website=[[WE Online]] |date=2013 |url=http://www.we-online.com/web/en/leiterplatten/layout/design_tipp/filling/filling_1.php |access-date=2017-12-18 |url-status=live |archive-url=https://web.archive.org/web/20171218141821/http://www.we-online.com/web/en/leiterplatten/layout/design_tipp/filling/filling_1.php |archive-date=2017-12-18}} |

* {{cite web |title=Via Filling - Overview of the variations |at=Printed Circuit Boards > Layout > Design Tip > Filling |publisher=[[Würth Elektronik GmbH & Co. KG]] |website=[[WE Online]] |date=2013 |url=http://www.we-online.com/web/en/leiterplatten/layout/design_tipp/filling/filling_1.php |access-date=2017-12-18 |url-status=live |archive-url=https://web.archive.org/web/20171218141821/http://www.we-online.com/web/en/leiterplatten/layout/design_tipp/filling/filling_1.php |archive-date=2017-12-18}} |

||

* {{cite web |title=Microvia Filling |at=Printed Circuit Boards > Layout > Design Tip > Microvia Filling |publisher=[[Würth Elektronik GmbH & Co. KG]] |website=[[WE Online]] |date=2015 |url=http://www.we-online.com/web/en/leiterplatten/layout/design_tipp/microvia_filling/microvia_filling.php |access-date=2017-12-18 |url-status=live |archive-url=https://web.archive.org/web/20171218141843/http://www.we-online.com/web/en/leiterplatten/layout/design_tipp/microvia_filling/microvia_filling.php |archive-date=2017-12-18}} |

* {{cite web |title=Microvia Filling |at=Printed Circuit Boards > Layout > Design Tip > Microvia Filling |publisher=[[Würth Elektronik GmbH & Co. KG]] |website=[[WE Online]] |date=2015 |url=http://www.we-online.com/web/en/leiterplatten/layout/design_tipp/microvia_filling/microvia_filling.php |access-date=2017-12-18 |url-status=live |archive-url=https://web.archive.org/web/20171218141843/http://www.we-online.com/web/en/leiterplatten/layout/design_tipp/microvia_filling/microvia_filling.php |archive-date=2017-12-18}} |

||

* {{cite web |author-first=Klaus |author-last1=Dingler |author-first2=Markus |author-last2=Musewski |title=Pluggen / Plugging |language=de |date=2009-03-18 |publisher=Fachverband Elektronik-Design e.V. (FED) |location=Berlin, Germany |website=FED-Wiki |url=http://wiki.fed.de/index.php/Pluggen_/_Plugging |access-date=2017-12-18 |url-status=live |archive-url=https://web.archive.org/web/20171218135704/http://wiki.fed.de/index.php/Pluggen_/_Plugging |archive-date=2017-12-18}} |

* {{cite web |author-first=Klaus |author-last1=Dingler |author-first2=Markus |author-last2=Musewski |title=Pluggen / Plugging |language=de |date=2009-03-18 |publisher=Fachverband Elektronik-Design e.V. (FED) |location=Berlin, Germany |website=FED-Wiki |url=http://wiki.fed.de/index.php/Pluggen_/_Plugging |access-date=2017-12-18 |url-status=live |archive-url=https://web.archive.org/web/20171218135704/http://wiki.fed.de/index.php/Pluggen_/_Plugging |archive-date=2017-12-18}} |

||

* {{cite web |title=Via Optimization Techniques for High-Speed Channel Designs |publisher=[[Altera Corporation]] |date=May 2008 |version=1.0 |type=Application note |id=AN-529-1.0 |url=https://www.altera.com/en_US/pdfs/literature/an/an529.pdf |access-date=2017-12-18 |url-status=live |archive-url=https://web.archive.org/web/20171218142832/https://www.altera.com/en_US/pdfs/literature/an/an529.pdf |archive-date=2017-12-18}} |

* {{cite web |title=Via Optimization Techniques for High-Speed Channel Designs |publisher=[[Altera Corporation]] |date=May 2008 |version=1.0 |type=Application note |id=AN-529-1.0 |url=https://www.altera.com/en_US/pdfs/literature/an/an529.pdf |access-date=2017-12-18 |url-status=live |archive-url=https://web.archive.org/web/20171218142832/https://www.altera.com/en_US/pdfs/literature/an/an529.pdf |archive-date=2017-12-18}} |

||

* {{cite web |title=Controlled Depth Drilling, or Back Drilling |work=Online Documentation for Altium Products |publisher=[[Altium]] |author-first=Jun |author-last=Chu |date=2017-04-11 |url=http://www.altium.com/documentation/17.0/display/ADES/((Controlled+Depth+Drilling,+or+Back+Drilling))_AD |access-date=2017-12-18 |url-status=live |archive-url=https://archive.today/20171218143321/http://www.altium.com/documentation/17.0/display/ADES/((Controlled%20Depth%20Drilling,%20or%20Back%20Drilling))_AD |archive-date=2017-12-18}} |

* {{cite web |title=Controlled Depth Drilling, or Back Drilling |work=Online Documentation for Altium Products |publisher=[[Altium]] |author-first=Jun |author-last=Chu |date=2017-04-11 |url=http://www.altium.com/documentation/17.0/display/ADES/((Controlled+Depth+Drilling,+or+Back+Drilling))_AD |access-date=2017-12-18 |url-status=live |archive-url=https://archive.today/20171218143321/http://www.altium.com/documentation/17.0/display/ADES/((Controlled%20Depth%20Drilling,%20or%20Back%20Drilling))_AD |archive-date=2017-12-18}} |

||

* {{cite web |title=Removing Unused Pads and Adding Teardrops |work=Online Documentation for Altium Products |publisher=[[Altium]] |author-first=Phil |author-last=Loughhead |date=2017-05-30 |url=http://www.altium.com/documentation/17.1/display/ADES/((Removing+Unused+Pads+and+Adding+Teardrops))_AD |access-date=2017-12-18 |url-status=live |archive-url=https://archive.today/20171218143719/http://www.altium.com/documentation/17.1/display/ADES/((Removing%20Unused%20Pads%20and%20Adding%20Teardrops))_AD |archive-date=2017-12-18}} |

* {{cite web |title=Removing Unused Pads and Adding Teardrops |work=Online Documentation for Altium Products |publisher=[[Altium]] |author-first=Phil |author-last=Loughhead |date=2017-05-30 |url=http://www.altium.com/documentation/17.1/display/ADES/((Removing+Unused+Pads+and+Adding+Teardrops))_AD |access-date=2017-12-18 |url-status=live |archive-url=https://archive.today/20171218143719/http://www.altium.com/documentation/17.1/display/ADES/((Removing%20Unused%20Pads%20and%20Adding%20Teardrops))_AD |archive-date=2017-12-18}} |

||

* {{cite book |author-last1=Brooks |author-first1=Douglas G. |author-last2=Adam |author-first2=Johannes |title=PCB Trace and Via Temperatures: The Complete Analysis |edition=2nd |publisher=CreateSpace Independent Publishing Platform |date=2017-02-09 |isbn=978-1541213524}} |

* {{cite book |author-last1=Brooks |author-first1=Douglas G. |author-last2=Adam |author-first2=Johannes |title=PCB Trace and Via Temperatures: The Complete Analysis |edition=2nd |publisher=CreateSpace Independent Publishing Platform |date=2017-02-09 |isbn=978-1541213524}} |

||

| Line 98: | Line 96: | ||

[[Category:Electronic design]] |

[[Category:Electronic design]] |

||

[[Category:Electronics manufacturing]] |

[[Category:Electronics manufacturing]] |

||

[[Category:Electrical connectors]] |

|||

[[Category:Printed circuit board manufacturing]] |

[[Category:Printed circuit board manufacturing]] |

||

Revision as of 14:53, 19 December 2024

(1) Through hole.

(2) Blind via.

(3) Buried via.

The gray and green layers are nonconducting, while the thin orange layers and red vias are conductive.

A via (Latin, 'path' or 'way') is an electrical connection between two or more metal layers of a printed circuit boards (PCB) or integrated circuit. Essentially a via is a small drilled hole that goes through two or more adjacent layers; the hole is plated with metal (often copper) that forms an electrical connection through the insulating layers.

Vias are an important concern in PCB manufacturing.[1] As vertical structures crossing multiple layers, they are specified differently from most of the design, which increases the chance for errors. They place the strictest demands on registration (how closely aligned different layers are). They are manufactured with different tooling from other features -- tooling that typically has looser tolerances. If either the hole or any layer is slightly out of place, the wrong electrical connections may be made; this may not be visible from the surface. After the hole is drilled, it must also be lined with conductive material, as opposed to simply leaving conductive material in place on copper layers. Even an initially good board may develop problems later because the via reacts to heat differently from the substrate around it. Vias also represent a discontinuity in the electrical impedance, which can cause problems for signal integrity.

In printed circuit boards

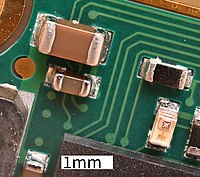

In printed circuit board (PCB) design, a via consists of two pads in corresponding positions on different copper layers of the board, that are electrically connected by a hole through the board.[citation needed] The hole is made conductive by electroplating, or is lined with a tube or a rivet.[citation needed] High-density multilayer PCBs may have microvias: blind vias are exposed only on one side of the board, while buried vias connect internal layers without being exposed on either surface. Thermal vias carry heat away from power devices and are typically used in arrays of about a dozen.[2][3]

A via consists of:

- Barrel — conductive tube filling the drilled hole

- Pad — connects each end of the barrel to the component, plane, or trace

- Antipad — clearance hole between barrel and metal layer to which it is not connected

A via, sometimes called PTV or plated-through-via, should not be confused with a plated through hole (PTH). A via is used as an interconnection between copper layers on a PCB while the PTH is generally made larger than vias and is used as a plated hole for acceptance of component leads - such as non-SMT resistors, capacitors, and DIP package IC. PTH can also be used as holes for mechanical connection while vias may not. Another usage of PTH is known as a castellated hole where the PTH is aligned at the edge of the board so that it is cut in half when the board is milled out of the panel - the main usage is for allowing one PCB to be soldered to another in a stack - thus acting both as a fastener and also as a connector.[4]

Three major kinds of vias are shown in right figure. The basic steps of making a PCB are: making the substrate material and stacking it in layers; through-drilling of plating the vias; and copper trace patterning using photolithography and etching. With this standard procedure, possible via configurations are limited to through-holes.[a] Depth-controlled drilling techniques such as using lasers can allow for more varied via types. Laser drills can also be used for smaller and more precisely positioned holes than mechanical drills produce. PCB manufacturing typically starts with a so-called core, a basic double-sided PCB. Layers beyond the first two are stacked from this basic building block. If two more layers are consecutively stacked from bottom of core, you can have a 1-2 via, a 1-3 via and a through hole. Each type of via is made by drilling at each stacking stage. If one layer is stacked on top of the core and other is stacked from the bottom, the possible via configurations are 1-3, 2-3 and through hole. The user must gather information about the PCB manufacturer's allowed methods of stacking and possible vias. For cheaper boards, only through holes are made and antipad (or clearance) is placed on layers which are supposed not to be contacted to vias.

IPC 4761

IPC 4761 defines the following via types:

- Type I: Tented via

- Type II: Tented & covered via

- Type III-a: Plugged via, sealed with non-conductive material on one side

- Type III-b: Plugged via, sealed with non-conductive material on both sides

- Type IV-a: Plugged & covered via, sealed with non-conductive material and covered with wet solder mask on one side

- Type IV-b: Plugged & covered via, sealed with non-conductive material and covered with wet solder mask on both sides

- Type V: Filled via, filled with non-conductive paste

- Type VI-a: Filled & covered via, covered with dry film or wet solder mask on one side

- Type VI-b: Filled & covered via, covered with dry film or wet solder mask on both sides

- Type VII: Filled & capped via, filled with non-conductive paste and overplated on both sides

Failure behavior

If well made, PCB vias will primarily fail due to differential expansion and contraction between the copper plating and the PCB in the out of plane direction (Z). This differential expansion and contraction will induce cyclic fatigue in the copper plating, eventually resulting in crack propagation and an electrical open circuit. Various design, material, and environmental parameters will influence the rate of this degradation.[5][6] To ensure via robustness, IPC sponsored a round-robin exercise that developed a time to failure calculator.[7]

Vias in integrated circuits

In integrated circuit (IC) design, a via is a small opening in an insulating oxide layer that allows a conductive connection between different layers. A via on an integrated circuit that passes completely through a silicon wafer or die is called a through-chip via or through-silicon via (TSV). Through-glass vias (TGV) have been studied by Corning Glass for semiconductor packaging, due to the reduced electrical loss of glass versus silicon packaging.[8] A via connecting the lowest layer of metal to diffusion or poly is typically called a "contact".

Gallery

-

Plated-through holes on a multilayer board (magnified)

-

Double layered plating in CAD. Vias makes EDA placement possible.

Bottom layer – Red

Top layer – Blue -

Plating of plated-through holes:

Above – Top layer

Down – Bottom layer

See also

- Through-hole technology (THT)

- Surface-mount technology (SMT)

- Through-silicon via (TSV)

- Via fence

- Feedthrough

Notes

- ^ Through-holes per core. It is possible, though more expensive, to create blind or buried vias by using additional cores and lamination steps. It is also possible to backdrill and remove the plating from one side through to the desired layer, which leaves the physical hole as a through-hole, but creates the electrical equivalent of a blind via. If a PCB needs enough layers to justify blind and buried vias, it is probably also using small enough traces packed tightly enough to require (laser-drilled) microvias.

References

- ^ "PCB Vias: An In-Depth Guide". ePiccolo Engineering.

- ^ "PCB design: A close look at facts and myths about thermal vias".

- ^ Gautam, Deepak; Wager, Dave; Musavi, Fariborz; Edington, Murray; Eberle, Wilson; Dunford, Willa G. (2013-03-17). A review of thermal management in power converters with thermal vias. 2013 Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC). Long Beach, California, U.S.A: IEEE. doi:10.1109/APEC.2013.6520276.

- ^ "Castellated Holes / Edge Plating PCB / Castellations". Hi-Tech Corp. 2011. Archived from the original on 2016-05-26. Retrieved 2013-01-02.

- ^ C. Hillman, Understanding plated through via failures, Global SMT & Packaging – November 2013, pp 26-28, https://www.dfrsolutions.com/hubfs/Resources/services/Understanding_Plated_Through_Via_Failures.pdf?t=1514473946162

- ^ C. Hillman, Reliable Plated Through Via Design and Fabrication, http://resources.dfrsolutions.com/White-Papers/Reliability/Reliable-Plated-Through-Via-Design-and-Fabrication1.pdf

- ^ "Plated Through Hole (PTH) Fatigue calculator". DfR Solutions. Retrieved 2017-12-17.

- ^ "Progress and Application of Through Glass Via (TGV) Technology" (PDF). corning.com. Retrieved 2019-08-08.

Further reading

- "Tips for PCB Vias Design" (PDF) (Technical note). Quick-teck. 2014. EN-00417. Retrieved 2017-12-18.

- "Via Tenting - Overview of the variations". WE Online. Würth Elektronik GmbH & Co. KG. 2014. Printed Circuit Boards > Layout > Design Tip > Tenting. Archived from the original on 2017-12-18. Retrieved 2017-12-18.

- "Via Plugging - Overview of the variations". WE Online. Würth Elektronik GmbH & Co. KG. 2014. Printed Circuit Boards > Layout > Design Tip > Plugging. Archived from the original on 2017-12-18. Retrieved 2017-12-18.

- "Via Filling - Overview of the variations". WE Online. Würth Elektronik GmbH & Co. KG. 2013. Printed Circuit Boards > Layout > Design Tip > Filling. Archived from the original on 2017-12-18. Retrieved 2017-12-18.

- "Microvia Filling". WE Online. Würth Elektronik GmbH & Co. KG. 2015. Printed Circuit Boards > Layout > Design Tip > Microvia Filling. Archived from the original on 2017-12-18. Retrieved 2017-12-18.

- Dingler, Klaus; Musewski, Markus (2009-03-18). "Pluggen / Plugging". FED-Wiki (in German). Berlin, Germany: Fachverband Elektronik-Design e.V. (FED). Archived from the original on 2017-12-18. Retrieved 2017-12-18.

- "Via Optimization Techniques for High-Speed Channel Designs" (PDF) (Application note). 1.0. Altera Corporation. May 2008. AN-529-1.0. Archived (PDF) from the original on 2017-12-18. Retrieved 2017-12-18.

- Chu, Jun (2017-04-11). "Controlled Depth Drilling, or Back Drilling". Online Documentation for Altium Products. Altium. Archived from the original on 2017-12-18. Retrieved 2017-12-18.

- Loughhead, Phil (2017-05-30). "Removing Unused Pads and Adding Teardrops". Online Documentation for Altium Products. Altium. Archived from the original on 2017-12-18. Retrieved 2017-12-18.

- Brooks, Douglas G.; Adam, Johannes (2017-02-09). PCB Trace and Via Temperatures: The Complete Analysis (2nd ed.). CreateSpace Independent Publishing Platform. ISBN 978-1541213524.

External links

- Online Via Calculator (Ampacity, Capacitance, Impedance, Power Dissipation Calculation).