Design rule checking: Difference between revisions

Ethan a dawe (talk | contribs) No edit summary |

Smartyhall (talk | contribs) |

||

| Line 4: | Line 4: | ||

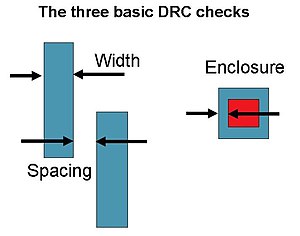

[[Image:BasicDRC.jpg|300px|right|thumb|The basic DRC checks - width, spacing, and enclosure]] |

[[Image:BasicDRC.jpg|300px|right|thumb|The basic DRC checks - width, spacing, and enclosure]] |

||

Design Rules are a series of parameters provided by [[Semiconductor fabrication|semiconductor manufacturer]]s that enable the designer to verify the correctness of |

Design Rules are a series of parameters provided by [[Semiconductor fabrication|semiconductor manufacturer]]s that enable the designer to verify the correctness of a [[mask set]]. Design rules are specific to a particular semiconductor manufacturing process. A design rule set specifies certain geometric and connectivity restrictions to ensure sufficient margins to account for variability in semiconductor manufacturing processes, so as to ensure that most of the parts work correctly. |

||

The most basic design rules are shown in the diagram on the right. The first are single layer rules. A ''width'' rule specifies the minimum width of any shape in the design. A ''spacing'' rule specifies the minimum distance between two adjacent objects. These rules will exist for each layer of semiconductor manufacturing process, with the lowest layers having the smallest rules (typically 100 nm as of 2007) and the highest metal layers having larger rules (perhaps 400 nm as of 2007). |

The most basic design rules are shown in the diagram on the right. The first are single layer rules. A ''width'' rule specifies the minimum width of any shape in the design. A ''spacing'' rule specifies the minimum distance between two adjacent objects. These rules will exist for each layer of semiconductor manufacturing process, with the lowest layers having the smallest rules (typically 100 nm as of 2007) and the highest metal layers having larger rules (perhaps 400 nm as of 2007). |

||

Revision as of 13:19, 25 December 2009

Design Rule Checking or Check(s) (DRC) is the area of Electronic Design Automation that determines whether the physical layout of a particular chip layout satisfies a series of recommended parameters called Design Rules. Design rule checking is a major step during Physical verification of the design, which also involves LVS (Layout versus schematic) Check, XOR Checks, ERC (Electrical Rule Check) and Antenna Checks. For advanced processes some fabs also insist upon the use of more Restrictive_Design_Rules to improve yield.

Design Rules

Design Rules are a series of parameters provided by semiconductor manufacturers that enable the designer to verify the correctness of a mask set. Design rules are specific to a particular semiconductor manufacturing process. A design rule set specifies certain geometric and connectivity restrictions to ensure sufficient margins to account for variability in semiconductor manufacturing processes, so as to ensure that most of the parts work correctly.

The most basic design rules are shown in the diagram on the right. The first are single layer rules. A width rule specifies the minimum width of any shape in the design. A spacing rule specifies the minimum distance between two adjacent objects. These rules will exist for each layer of semiconductor manufacturing process, with the lowest layers having the smallest rules (typically 100 nm as of 2007) and the highest metal layers having larger rules (perhaps 400 nm as of 2007).

A two layer rule specifies a relationship that must exist between two layers. For example, an enclosure rule might specify that an object of one type, such as a contact or via, must be covered, with some additional margin, by a metal layer. A typical value as of 2007 might be about 10 nm.

There are many other rule types not illustrated here. A minimum area rule is just what the name implies. Antenna rules are complex rules that check ratios of areas of every layer of a net for configurations that can result in problems when intermediate layers are etched. Many other such rules exist and are explained in detail in the documentation provided by the semiconductor manufacturer.

Academic design rules are often specified in terms of a scalable parameter, λ, so that all geometric tolerances in a design may be defined as integer multiples of λ. This simplifies the migration of existing chip layouts to newer processes. Industrial rules are more highly optimized, and only approximate uniform scaling. Design rule sets have become increasingly more complex with each subsequent generation of semiconductor process.

Design Rule Checking Software

The main objective of design rule checking (DRC) is to achieve a high overall yield and reliability for the design. If design rules are violated the design may not be functional. To meet this goal of improving die yields, DRC has evolved from simple measurement and Boolean checks, to more involved rules that modify existing features, insert new features, and check the entire design for process limitations such as layer density. A completed layout consists not only of the geometric representation of the design, but also data that provides support for the manufacture of the design. While design rule checks do not validate that the design will operate correctly, they are constructed to verify that the structure meets the process constraints for a given design type and process technology.

DRC software usually takes as input a layout in the GDSII standard format and a list of rules specific to the semiconductor process chosen for fabrication. From these it produces a report of design rule violations that the designer may or may not choose to correct. Carefully "stretching" or waiving certain design rules is often used to increase performance and component density at the expense of yield.

DRC products define rules in a language to describe the operations needed to be performed in DRC. For example, Mentor Graphics uses Standard Verification Rule Format (SVRF) language in their DRC rules files and Magma Design Automation is using TCL-based language. A set of rules for a particular process is referred to as a run-set, rule deck, or just a deck.

DRC is a very computationally intense task. Usually DRC checks will be run on each sub-section of the ASIC to minimise the number of errors that are detected at the top level. If run on a single CPU, customers may have to wait up to a week to get the result of a Design Rule check for modern designs. Most design companies require DRC to run in less than a day to achieve reasonable cycle times since the DRC will likely be run several times prior to design completion. With today's processing power, full-chip DRC's may run in much shorter times as quick as one hour depending on the chip complexity and size.

Some example of DRC's in IC design include:

- Active to active spacing

- Well to well spacing

- Minimum channel length of the transistor

- Minimum metal width

- Metal to metal spacing

- Metal fill density (for processes using CMP)

- ESD and I/O rules

Commercial DRC Software

Major products in the DRC area of EDA are:

- "ALINT" by ALDEC

- "HiPer Verify" by Tanner EDA

- Calibre by Mentor Graphics

- Hercules by Synopsys

- Dracula and Assura by Cadence Design Systems

- Quartz by Magma Design Automation

- Advanced Design System Design Rule Checker by Agilent's EEsof EDA division

- Some semiconductor companies have their own proprietary DRC software.

All these companies are working on versions that run on many CPUs, to dramatically reduce the elapsed time required.

Estimated annual sales of DRC software are in the $200 to $300 million range.[citation needed] The cost of a single site license of semiconductor EDA software, including DRC components, may exceed $1 million.[citation needed]

References

- Electronic Design Automation For Integrated Circuits Handbook, by Lavagno, Martin, and Scheffer, ISBN 0-8493-3096-3 A survey of the field, from which part of the above summary were derived, with permission.