Duron: Difference between revisions

No edit summary |

|||

| Line 30: | Line 30: | ||

==Performance== |

==Performance== |

||

The original Duron processors were derived from AMD's mainstream ''Athlon'' [[Athlon#Athlon Thunderbird|Thunderbird]] processors, the primary difference being a reduction in L2 cache size to 64 [[Binary prefix|KB]] from the Athlon's 256 KB. This was a relatively severe reduction, making it even smaller than the 128 KB L2 available on Intel's competing budget [[Celeron]] line. However, the originating Thunderbird architecture already featured one of the largest L1 caches at 128 KB (which was not reduced in the Duron) and also introduced AMD's switch to an exclusive cache design which effectively unified the L1 and L2 caches. Because of this, the Duron behaved as if it had a high speed 128 KB cache combined with a somewhat slower 64 KB segment giving an effective 192 KB cache, |

The original Duron processors were derived from AMD's mainstream ''Athlon'' [[Athlon#Athlon Thunderbird|Thunderbird]] processors, the primary difference being a reduction in L2 cache size to 64 [[Binary prefix|KB]] from the Athlon's 256 KB. This was a relatively severe reduction, making it even smaller than the 128 KB L2 available on Intel's competing budget [[Celeron]] line. However, the originating Thunderbird architecture already featured one of the largest L1 caches at 128 KB (which was not reduced in the Duron) and also introduced AMD's switch to an exclusive cache design which effectively unified the L1 and L2 caches. Because of this, the Duron behaved as if it had a high speed 128 KB cache combined with a somewhat slower 64 KB segment giving an effective 192 KB cache, versus the traditional inclusive cache design where the L2 cache had to store a duplicate of the data stored in the L1 cache. As a comparison the inclusive design of the Celeron effectively reduced the available size of the Level 2 cache by the size of the Level 1, which resulted in an effective size of 96 KB (128-32) in contrast to the Duron's exclusive design (128+64=192). |

||

Consequently, the Duron inherited the Thunderbird's reduction in sensitivity to L2 cache size, allowing AMD to make their L2 cache higher latency and lower bandwidth to lessen processor complexity and allow better manufacturing [[Semiconductor device fabrication#Device test|yields]] without incurring a significant performance loss. The net result was that the budget Duron "Spitfire" CPU was roughly only 10% slower than an equivalently clocked (and significantly more expensive) Athlon "Thunderbird". |

Consequently, the Duron inherited the Thunderbird's reduction in sensitivity to L2 cache size, allowing AMD to make their L2 cache higher latency and lower bandwidth to lessen processor complexity and allow better manufacturing [[Semiconductor device fabrication#Device test|yields]] without incurring a significant performance loss. The net result was that the budget Duron "Spitfire" CPU was roughly only 10% slower than an equivalently clocked (and significantly more expensive) Athlon "Thunderbird". |

||

Revision as of 03:36, 21 December 2018

This article includes a list of references, related reading, or external links, but its sources remain unclear because it lacks inline citations. (January 2013) |

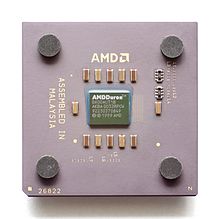

AMD Duron "Spitfire" 600MHz CPU | |

| General information | |

|---|---|

| Launched | mid 2000 |

| Discontinued | 2004 |

| Common manufacturer |

|

| Performance | |

| Max. CPU clock rate | 600 MHz to 1.8 GHz |

| FSB speeds | 200 MT/s to 266 MT/s |

| Architecture and classification | |

| Technology node | 0.18µm to 0.13µm |

| Instruction set | x86 |

| Physical specifications | |

| Socket | |

| Products, models, variants | |

| Core names |

|

| History | |

| Successor | Sempron |

AMD Duron refers to a line of budget x86-compatible microprocessors manufactured by AMD. Released on June 19, 2000 as a lower-cost offering to complement AMD's then mainstream performance Athlon processor line, it also competed with rival chipmaker Intel's Pentium III and Celeron processor offerings. The Duron brand name was retired in 2004, succeeded by the Sempron line of processors as AMD's budget offering.

Performance

The original Duron processors were derived from AMD's mainstream Athlon Thunderbird processors, the primary difference being a reduction in L2 cache size to 64 KB from the Athlon's 256 KB. This was a relatively severe reduction, making it even smaller than the 128 KB L2 available on Intel's competing budget Celeron line. However, the originating Thunderbird architecture already featured one of the largest L1 caches at 128 KB (which was not reduced in the Duron) and also introduced AMD's switch to an exclusive cache design which effectively unified the L1 and L2 caches. Because of this, the Duron behaved as if it had a high speed 128 KB cache combined with a somewhat slower 64 KB segment giving an effective 192 KB cache, versus the traditional inclusive cache design where the L2 cache had to store a duplicate of the data stored in the L1 cache. As a comparison the inclusive design of the Celeron effectively reduced the available size of the Level 2 cache by the size of the Level 1, which resulted in an effective size of 96 KB (128-32) in contrast to the Duron's exclusive design (128+64=192).

Consequently, the Duron inherited the Thunderbird's reduction in sensitivity to L2 cache size, allowing AMD to make their L2 cache higher latency and lower bandwidth to lessen processor complexity and allow better manufacturing yields without incurring a significant performance loss. The net result was that the budget Duron "Spitfire" CPU was roughly only 10% slower than an equivalently clocked (and significantly more expensive) Athlon "Thunderbird".

Compatibility

The Duron line was pin-compatible and operated on the same motherboards as the Athlon line, requiring only a BIOS update in most cases. The original Duron was introduced with a 100 MHz (effectively 200 MHz) front-side bus - the same as the then current Socket A Athlons. Later with the introduction of motherboard chipsets offering higher FSB speeds of 133 MHz (FSB 266) and AMD's matching introduction of Athlon "C" processors supporting this speed, the Duron initially retained the 100 MHz FSB for purposes of market segmentation. Later Durons were given official support for 133 MHz bus operation only after the Athlon XP was used to introduce 166/200 MHz FSB (FSB 333/400) speeds.

Revisions

The original Duron, using the "Spitfire" core, was manufactured in 2000 and 2001 at speeds ranging from 600 to 950 MHz. It was based on the 180 nm "Thunderbird" Athlon core.

The second-generation Duron, the "Morgan" core, was sold in speed grades between 900 and 1300 MHz, and was based on the 180 nm "Palomino" Athlon XP core. As a result, it featured a few important enhancements, namely full Intel SSE support, enlarged TLBs, hardware data prefetch, and an integrated thermal diode. Like the "Palomino" core, "Morgan" was also expected to reduce heat dissipation; however in "Morgan"'s case this did not happen due to its increased core voltage.

The final generation Duron was called "Applebred", sometimes called "Appalbred", and was based on the "Appaloosa" Duron along with the 130 nm "Thoroughbred" Athlon XP. "Appaloosa" was never officially announced but it did see very limited circulation.

Enthusiasts

Duron was often a favorite of computer builders looking for performance while on a tight budget. In 2003, the "Applebred" Duron was available in 1.4 GHz, 1.6 GHz and 1.8 GHz forms, all on a 133 MHz (FSB 266) bus by default. Enthusiast groups quickly discovered these Durons to be rebadged "Thoroughbred" A/B cores with some cache disabled (and perhaps defective). With a basic chip configuration modification, it was found that "Applebred" Durons could be turned into "Thoroughbred B" Athlon XPs, with full 256KB cache, with a very high success rate. However, this was only possible for a period of approximately 4 weeks, as shortly after "Applebred" was released, AMD changed the chip configuration method to one that was not changeable.

Duron core data

Spitfire (Model 3, 180 nm)

- L1-Cache: 64 + 64 KB (Data + Instructions)

- L2-Cache: 64 KB, full speed

- MMX, Extended MMX, 3DNow!, Extended 3DNow!

- Socket A (EV6)

- Front side bus: 100 MHz (200 MT/s)

- VCore: 1.50 V - 1.60 V

- First release: June 19, 2000

- Clockrate: 600 MHz - 950 MHz

Morgan (Model 7, 180 nm)

- L1-Cache: 64 + 64 KB (Data + Instructions)

- L2-Cache: 64 KB, full speed

- MMX, Extended MMX, 3DNow!, Extended 3DNow!, SSE

- Socket A (EV6)

- Front side bus: 100 MHz (200 MT/s)

- VCore: 1.7-1.75 V

- First release: August 20, 2001

- Clockrate: 900 MHz - 1300 MHz

Applebred (Model 8, 130 nm)

- L1-Cache: 64 + 64 KB (Data + Instructions)

- L2-Cache: 64 KB, full speed

- MMX, Extended MMX, 3DNow!, Extended 3DNow!, SSE

- Socket A (EV6)

- Front side bus: 133 MHz (266 MT/s)

- VCore: 1.50 V

- First release: August 21, 2003

- Clockrate: 1400, 1600, 1800 MHz

See also

List of AMD Duron microprocessors

References

- "AMD Duron (64 KB integrated Level 2 cache)" by Anthony Barrett, Processor Emporium, retrieved January 13, 2006

- "cpu-museum.de New additions to the museum (Appalbred)", by Christian "Grampa", January 7, 2004, retrieved January 9, 2006, Archived at the Wayback Machine (archived July 18, 2011)

- "IA-32 implementation AMD K7 (inclusive on Slot A)" by Sandpile.org, retrieved January 9, 2006

- "Press Release: AMD Athlon Processor Performance-Enhancing Cache Memory" by AMD, June 4, 2000, retrieved January 13, 2006

External links

- Budget CPU Shootout - Popular hardware review website Anandtech compares low priced CPUs

- cpu-collection.de AMD Duron processor images and descriptions

- [1] Updated CPU Cheatsheet - Seven Years of Covert CPU Operations