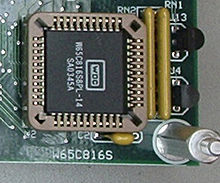

WDC 65C816

PDIP40 package | |

| General information | |

|---|---|

| Launched | 1985 |

| Common manufacturer |

|

| Performance | |

| Max. CPU clock rate | 1 MHz to 14 MHz |

| Data width |

|

| Address width | 24 |

| Architecture and classification | |

| Instruction set | 6502 |

| Number of instructions | 92 |

| Physical specifications | |

| Packages | |

| History | |

| Predecessors |

|

The W65C816S (also 65C816 or 65816) is a 16-bit microprocessor (MPU) developed and sold by the Western Design Center (WDC). Introduced in 1983,[1] the W65C816S is an enhanced version of the WDC 65C02 8-bit MPU, itself a CMOS enhancement of the venerable MOS Technology 6502 NMOS MPU. The 65C816 is the CPU for the Apple IIGS and, in modified form, the Super Nintendo Entertainment System.

The 65 in the part's designation comes from its 65C02 compatibility mode, and the 816 signifies that the MPU has selectable 8- and 16-bit register sizes. In addition to the availability of 16-bit registers, the W65C816S extends memory addressing to 24 bits, supporting up to 16 megabytes of random-access memory. It has an enhanced instruction set and a 16-bit stack pointer, as well as several new electrical signals for improved system hardware management.

At reset, the W65C816S starts in "emulation mode", meaning it substantially behaves as a 65C02. Thereafter, the W65C816S may be switched to "native mode" with a two instruction sequence, causing it to enable all enhanced features, yet still maintain a substantial degree of backward compatibility with most 65C02 software. However, unlike the PDIP40 version of the 65C02, which is a pin-compatible replacement for its NMOS ancestor, the PDIP40 W65C816S is not pin-compatible with any other 6502 family MPU.

The W65C802 is completely software-compatible with the 65C816, but is electrically-compatible with the 6502 and 65C02. Hence the 65C802 could be used as a drop-in replacement in most systems equipped with a 6502 or 65C02. However, the 65C802 cannot emit a 24-bit address, which limits it to a 64 KB address space. The 65C802 is no longer produced.

History

In 1981, Bill Mensch, founder and CEO of WDC, began development of the 65C02 with his production partners, primarily Rockwell Semiconductor and Synertek. The primary goal of the 65C02 effort was to move from the original 6502's NMOS process to the CMOS process, which would allow it to run at much lower power levels, somewhere between 1⁄10 and 1⁄20 at any given clock speed. Also desired was the ability to raise the maximum supported clock speed. The 65C02 design addressed chip errata present in the NMOS 6502 (e.g., the infamous JMP (<addr>) bug) and introduced new instructions and new addressing modes for some existing instructions.[2]

Development of the W65C816S commenced in 1982 after Mensch consulted with Apple Computer on a new version of the Apple II series of personal computers that would, among other things, have improved graphics and sound. Apple wanted an MPU that would be software compatible with the 6502 then in use in the Apple II but with the ability to address more memory, and to load and store 16 bit words. The result was the 65C816, finished in March 1984, with samples provided to both Apple and Atari in the second half of the year and full release in 1985.[3] Mensch was aided during the design process by his sister Kathryn, who was responsible for part of the device's layout.

The same process also led to the 65C802, which was identical inside to the 65C816. Both were produced on the same fabrication lines and diverged only during the last metalization stages when the chip was being connected to the external pins. In the 65C802, those pins had the same layout as the original 6502, which allowed it to be used as a drop-in replacement while still allowing the 16-bit processing of the CPU to be used. However, as it used the original pinout it had only 16 addressing pins, and could therefore only access 64 KB of external memory.[4] Typically, when hardware manufacturers designed a project from the ground up, they used the 65C816 rather than the 65C802, resulting in the latter being withdrawn from production.

Apple subsequently integrated the 65C816 into the Apple IIGS computer. The basic 65C816 design was second-sourced by GTE, Sanyo and others from the mid-to-late 1980s to the early 1990s.

In the 1990s, both the 65C816 and 65C02 were converted to a fully static core, which made it possible to completely stop the processor's Ø2 clock without loss of register contents. This feature, along with the use of asynchronous static RAM, made it possible to produce designs that used minimal power when in a standby state.

As of 2023[update], the W65C816S is available from WDC in 40 pin PDIP, PLCC44, or 44-pin TQFP packaging, as well as a core for ASIC integration (for example Winbond's W55V9x series of TV Edutainment ICs). WDC, itself a fabless semiconductor company, works with various foundries to produce the W65C816S, as well as other compatible products. Discrete processors are available through a number of electronics distributors. For designers who wish to include W65C816S functionality into a custom ASIC, WDC offers RTL (register-transfer level) code in Verilog.

Features

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

WDC 65c816 features:

- Fully static CMOS design offers low power consumption (300 µA at 1 MHz) and increased noise immunity.

- Wide operating voltage range: 1.8 V to 5.0 V ± 5%.

- Wide operating frequency range, officially 14 MHz maximum at 5 volts (20Mhz in SuperCPU), using a single-phase clock source (hobbyists have successfully operated the 65C816 well beyond 20 MHz).

- Emulation mode allows substantial software compatibility with the NMOS 6502 and CMOS 65C02, excepting undocumented opcodes. All 256 opcodes in the 65C816 are functional in both operating modes.

- 24-bit memory addressing provides access to 16 MB of memory space.

- 16-bit ALU, accumulator (

C), stack pointer (SP), and index registers (XandY). - 16-bit direct page (aka zero page) register (

DP). - 8-bit data bank (

DB) and program bank (PB) registers, generating bits 16–23 of 24-bit code and data addresses. Separate program and data bank registers allow program segmentation and 16 MB linear data addressing. - Valid data address (

VDA) and valid program address (VPA) control outputs for memory qualification, dual cache and cycle steal DMA implementation. - Vector pull (

VPB) control output to indicate when an interrupt vector is being fetched. - Abort (

ABORTB) input and associated vector supports processor repairs of bus error conditions, such as page faults and memory access violations. - Direct page register and stack relative addressing provides capability for reentrant, recursive and re-locatable programming.

- 24 addressing modes—13 original 6502 modes with 92 instructions using 256 op codes, including most new opcodes implemented in the 65C02.

- Block-copy instructions (

MVNandMVP), allowing rapid copying of data structures from one area of RAM to another with minimal code. - Wait-for-Interrupt (

WAI) and Stop-the-Clock (STP) instructions further reduce power consumption, decrease interrupt latency and allow synchronization with external events. - Co-Processor (

COP) instruction with associated vector supports co-processor configurations, e.g., floating point processors. - Reserved "escape" (

WDM) instruction for future two-byte opcodes and a link to future designs (WDM are the initials of W65C816S designer William D. Mensch).

Comparison with earlier models

Two modes

The 65C816 has two operating modes: "emulation mode", in which the 16-bit operations are invisible—the index registers are forced to eight bits—and the chip appears to be very similar to the 6502, with the same cycle timings for the opcodes; and "native mode", which exposes all new features. The CPU automatically enters emulation mode when it is powered on or reset, which allows it to replace a 65(C)02, assuming one makes the required circuit changes to accommodate the different pin layout.[2]

16-bit registers

The most obvious change to the 65C816 when running in native mode is the expansion of the various registers from 8-bit to 16-bit sizes. This enhancement affects the accumulator (A), the X and Y index registers, and the stack pointer (SP). It does not affect the program counter (PC), which has always been 16-bit.[5]

When running in native mode, two bits in the status register change their meaning. In the original 6502, bits 4 and 5 were not used, although bit 4 is referred to as the break (b) flag. In native mode, bit 4 becomes the x flag and bit 5 becomes the m flag. These bits control whether or not the index registers (x) and/or accumulator/memory (m) are 8-bit or 16-bit in size. Zeros in these bits set 16-bit sizes, ones set 8-bit sizes. These bits are locked at ones when the processor is powered on or reset, but become changeable when the processor is switched to native mode.[5]

In native mode operation, the accumulator and index registers may be set to 16- or 8-bit sizes at the programmer’s discretion by using the REP and SEP instructions to manipulate the m and x status register bits. This feature gives the programmer the ability to perform operations on either word- and byte-size data. As the accumulator and index register sizes are independently settable, it is possible, for example, to have the accumulator set to eight bits and the index registers set to 16 bits, giving the programmer the ability to manipulate individual bytes over a 64KB range without having to perform pointer arithmetic.

When register sizes are set to 16 bits, a memory access will fetch or store two contiguous bytes at the rate of one byte per clock cycle. Hence a read-modify-write instruction, such as ROR <addr>, when used while the accumulator is set to 16 bits, will affect two contiguous bytes of memory, not one and will consume more clock cycles than when the accumulator is set to eight bits. Similarly, all arithmetic and logical operations will be 16-bit operations.[6]

24-bit addressing

The other major change to the system while running in native mode is that the memory model is expanded to a 24-bit format from the original 16-bit format of the 6502. The 65c816 makes use of two 8-bit registers, the data bank register (DB) and the program bank register (PB), to set bits 16-23 of the address, effectively generating 24-bit addresses. In both cases, 'bank' refers to a contiguous 64 KB segment of memory that is bounded by the address range $xx0000-$xxFFFF, where xx is the bank address, that is, bits 16-23 of the effective address. Both DB and PB are initialized to $00 at power-on or reset.[7]

During an opcode or operand fetch cycle, PB is prepended to the program counter (PC) to form the 24-bit effective address. Should PC "wrap" (return to zero), PB will not be incremented. Hence a program is bounded by the limits of the bank in which it is executing. Implied by this memory model is that branch and subroutine targets must be in the same bank as the instruction making the branch or call, unless "long" jumps or subroutine calls are used to execute code in another bank. There is no programmatic means by which PB can be directly changed.[8]

During a data fetch or store cycle, DB is prepended to a 16-bit data address to form the 24-bit effective address at which data will be accessed. This processor characteristic makes it possible to sanely execute 6502 or 65c02 code that uses 16-bit addresses to reference data elements. Unlike PB, DB can be changed under program control, something that might be done to access data beyond the limits of 16-bit addressing. Also, DB will temporarily increment if an address is indexed beyond the limits of the bank currently in DB. DB is ignored if a 24-bit address is specified as the operand to a data fetch/store instruction, or if the effective address is on direct (zero) page or the hardware stack. In the latter case, an implied bank $00 is used to generate the effective address.[9]

A further addition to the register set is the 16-bit direct page register (DP), which sets the base address for what was formerly called the zero page, but now referred to as direct page. Direct page addressing uses an 8-bit address, which results in faster access than when a 16- or 24-bit address is used. Also, some addressing modes that offer indirection are only possible on direct page. In the 65(c)02, the direct page is always the first 256 bytes of memory, hence “zero page”. In native mode, the 65c816 can relocate direct (zero) page anywhere in bank $00 (the first 64 KB of memory) by writing the 16-bit starting address into DP. There is a one-cycle access penalty if DP is not set to an exact page boundary, that is, if the value in DP is not $xx00, where xx is the most-significant byte.[10]

Switching between modes

The current mode of operation is stored in the emulation (e) bit. Having already added the new x and m bits to the previous set of six flags in the status register (SR), there were not enough bits left to hold the new mode bit. Instead, a unique solution was used in which the mode bit was left "invisible", unable to be directly accessed. The XCE (eXchange Carry with Emulation) instruction exchanges the value of the emulation bit with the carry (c) bit, bit 0 in SR. For instance, if one wants to enter native mode after the processor has started up, one would use CLC to clear the carry bit, and then XCE to write it to the emulation bit.[11] Returning to 65c02 emulation mode uses SEC followed by XCE.[12]

Internally, the 65c816 is a fully 16-bit design. The m and x bits in SR determine how the user registers (accumulator and index) appear to the rest of the system. Upon reset, the 65c816 starts in 6502 emulation mode, in which m and x are locked to 1. Hence the registers are locked to eight-bit size. The most significant byte (MSB) of the accumulator (the B-accumulator) is not directly accessible but can be swapped with the least significant byte (LSB) of the accumulator (the A-accumulator) by using the XBA instruction. There is no corresponding operation for the index registers (X and Y), whose MSBs are locked at $00.

Upon being switched to native mode, the MSB of X and Y will be zero, and the B-accumulator will be unchanged. If the m bit in SR is cleared, the B-accumulator will be “ganged” to the A-accumulator to form a 16-bit register (called the C-accumulator). A load/store or arithmetic/logical operation involving the accumulator and/or memory will be a 16-bit operation—two bus cycles are required to fetch/store a 16-bit value.

If the x bit in SR is cleared, both index registers will be set to 16 bits. If used to index an address, e.g., LDA SOMEWHERE,X, the 16-bit value in the index register will be added to the base address to form the effective address.

If the m bit in SR is set the accumulator will return to being an 8-bit register and subsequent operations on the accumulator, with a few exceptions, will be 8-bit operations. The B-accumulator will retain the value it had when the accumulator was operating in 16-bit mode. The exceptions are the instructions that transfer the direct page register (DP) and stack pointer (SP) to/from the accumulator. These operations are always 16-bits wide in native mode, regardless of the condition of the m bit in SR.

If the x bit in SR is set, not only will the index registers return to being 8 bits, whatever was in the MSB while in 16-bit mode will be lost, something an assembly language programmer cannot afford to forget.[13]

Applications

Systems based on 65c816 variants:

- Acorn Communicator

- Apple IIGS

- C-One and SuperCPU enhancements for the Commodore 64

- Super Nintendo Entertainment System: the console's Ricoh 5A22 CPU is based on the 65c816.

- Additionally, 30+ Super NES games include the Nintendo SA1, a 65c816-based co-processor chip, in each cartridge.

- C256 Foenix's U/U+ model[14] and F256K model[15]

See also

References

Citations

- ^ Chronology of Microprocessors (1980–1989)

- ^ a b Eyes & Lichty 1986, p. 42.

- ^ Eyes & Lichty 1986, p. 44.

- ^ Eyes & Lichty 1986, p. 45.

- ^ a b Eyes & Lichty 1986, p. 46.

- ^ Eyes & Lichty 1986, p. 52.

- ^ Eyes & Lichty 1986, p. 53.

- ^ Eyes & Lichty 1986, p. 54.

- ^ Eyes & Lichty 1986, p. 55.

- ^ Eyes & Lichty 1986, p. 80.

- ^ Eyes & Lichty 1986, p. 64.

- ^ Eyes & Lichty 1986, p. 65.

- ^ Eyes & Lichty 1986, p. 51.

- ^ "16bits CPU – New Retro Computers". Foenix Retro Systems.

- ^ "F256K". Foenix Retro Systems.

Bibliography

- Eyes, David; Lichty, Ron (1986). Programming the 65816 - including the 6502, 65C02, 65802. Prentice Hall. ISBN 978-0893037895.

Further reading

- 65C816 Datasheet; Western Design Center; 55 pages; 2018.

External links

- 65C816 webpage - Western Design Center

- 6502/65C02/65C816 Instruction Set decoded

- 65816/65C816 Technical Documents - zophar.net

- A 6502 Programmer's Introduction to the 65816 – A Commodore World article by Brett Tabke; includes CMD's instruction set summary

- Investigating 65C816 Interrupts – An extensive discussion of interrupt processing on the 65C816