锁相环:修订间差异

小无编辑摘要 |

小 →应用领域 标签:加入不存在模板 |

||

| 第106行: | 第106行: | ||

* 非接觸式的[[原子力显微镜]],偵測探針和表面的交叉作用產生的共振頻率。 |

* 非接觸式的[[原子力显微镜]],偵測探針和表面的交叉作用產生的共振頻率。 |

||

* [[直流电动机]][[电机控制器]] |

* [[直流电动机]][[电机控制器]] |

||

===時脈恢復=== |

|||

有些資料流,特別是高速的串列資料流(例如硬碟磁頭讀到的原始資料流),在傳送時不會將其時脈信號一起送出。接收器利用類似的參考頻率來產生時脈,再利用PLL將其時脈和接收資料的相位鎖定同步。此程序稱為{{le|時脈恢復|clock recovery}}。為了時脈功能,資料流中必須有夠快的資料切換,以校正PLL振盪器的頻率飄移。一般而言,會使用一些[[线路码]](例如[[8b/10b]]),讓二次資料切換時間間隔有一個明確的上限值。 |

|||

=== 偏移校正=== |

|||

若時脈和資料一起傳送,會用時脈為準來進行資料取樣。因為時脈接收後需放大,才能驅動正反器取樣資料。時脈邊緣和接收的資料窗之間會有一個有限大小的時間延遲,長度隨過程、溫度、電壓而不同。此時間延遲會限制傳送資料的速率。有一種消除延遲的方式是在接收端加入一個偏移校正(deskew)的PLL,使得每一次資料正反器的時脈都接收到的時間同相位。此應用中,常會使用一種特殊的锁相环,稱為{{延遲鎖相環|delay-locked loop}}(DLL)<ref>{{cite web |

|||

|url = http://www-vlsi.stanford.edu/papers/mh_micro_98.pdf |

|||

|author1 = M Horowitz |

|||

|author2 = C. Yang |

|||

|author3 = S. Sidiropoulos |

|||

|title = High-speed electrical signaling: overview and limitations |

|||

|publisher = IEEE Micro |

|||

|date = 1998-01-01 |

|||

|url-status = dead |

|||

|archive-url = https://web.archive.org/web/20060221015031/http://www-vlsi.stanford.edu/papers/mh_micro_98.pdf |

|||

|archive-date = 2006-02-21 |

|||

}}</ref>。 |

|||

==相關條目== |

==相關條目== |

||

2021年4月20日 (二) 14:39的版本

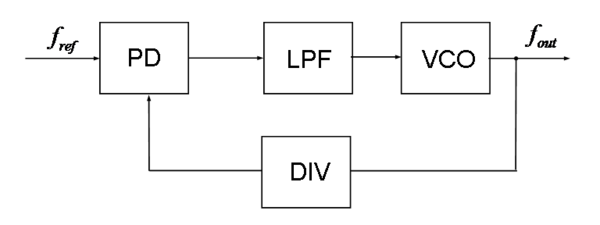

鎖相迴路(PLL: Phase-locked loops)是利用反馈(Feedback)控制原理实现的频率及相位的控制系統,其作用是将电路输出的信號与其外部的参考信號保持同步,当参考信號的频率或相位发生改变时,鎖相迴路会检测到这种变化,并且通过其内部的反馈系统来调节输出频率,直到两者重新同步,这种同步又称为“鎖相”(Phase-locked)。

鎖相迴路有許多種,最簡單的鎖相迴路會包括變頻振盪器以及鉴相器,形成反馈迴路。振盪器產生訊號,鉴相器比較輸出訊號和輸入週期訊號之間的相位,調整振盪器輸出,設法和輸入週期訊號同步。

若讓輸出訊號和輸入訊號之間的相位一致,則兩者的頻率也會一致。因此,鎖相迴路除了讓相位一致之外,也可以追蹤輸入訊號的頻率,或是產生頻率是輸入訊號整數倍的信號。此特性可以用在電腦時脈的同步、解調變及頻率合成。

鎖相迴路常用在无线电、电信、电子计算机及其他電子設備中。鎖相迴路也可以用來解調變訊號、從高雜訊的通訊頻道中恢復原始信號、產生頻率為輸入信號頻率整數倍的頻率(頻率合成)、或在數位電路(例如微处理器)中產生準確的時鐘脈衝。因為單一的集成电路即可提供完整的鎖相迴路機能,此技術已普遍使用在現在的電子設備中,輸出頻率從1Hz以下,到數GHz。

實際上類似的例子

賽車

锁相环可以用賽車來說明:考慮兩部車進行的繞圈賽車,一部車代表輸入信號,另一部車代表锁相环的輸出,也就是壓控振盪器(VCO)頻率。每一圈代表一個完整的週期。每小時的圈數代表頻率,兩部車之間的距離代表信號之間的相位差。

大部份賽車的過程中,兩部車都可以超過對方或落過對方,這類似锁相环的非鎖相狀態。

但若有事故,賽車場會出現黃色警告旗,此時,任何一部車輛都不允許超過其他的車,也不允許被其他的車超過。此時的兩部車就代表锁相环在鎖相狀態下的輸入信號和輸出信號。每一個駕駛者都會量測其車輛和其他車輛的相位差。若和前車保持的距離太遠了,會設法加速使距離拉近,若和前車保持的距離太近了,會設法減速使距離拉遠。因此,兩部車會保持固定的距離。因為車輛不允許超過其他的車,因此在相同時間內,兩車繞的圈數會相同,因此兩個信號的頻率相同。

時鐘的例子

相位和時間成正比[a],因此相位差可以用時間差來表示。時鐘相對其他時鐘而言,某程度上會有鎖相(固定時間差),但準確度可能有些不同。

若讓時鐘自行運作,各時鐘計時的速率會有些微的差距。例如牆上的鐘每一小時可能會比國家標準技術研究所的鐘快了幾秒,隨著時間過去,時間差會越來越大。

若要讓牆上的鐘和參考時鐘同步,可能每一週會比較牆上的鐘和參考時鐘的時間(相位比較),然後調整牆上的鐘。若沒有調整,牆上的鐘和參考時鐘的偏差會越來越大。

有些時鐘有計時調整功能,若比較時鐘和標準時鐘,發現時鐘太快了,會設法讓時鐘的計時慢一點,若時鐘太慢了,會設法讓時鐘的計時快一點。若順利的話,時鐘和標準時鐘的誤差會漸漸縮小。幾週後,時鐘就會準確的對應標準時鐘(在時鐘本身的穩定性範圍內,頻率和相位都和標準時鐘一致)。

早期电动机械学中也有锁相环,例如1921年的Shortt-Synchronome鐘。

歷史

丹麥物理學家克里斯蒂安·惠更斯早在1673年就發現弱耦合的摆钟會有自發性同步的情形[1]。在19世紀時,第三代瑞利男爵約翰·斯特拉特發現弱耦合的風琴管及音叉也有同步的情形[2]。1919年時,威廉·埃克爾斯和J. H. Vincent發現二個調諧到頻率略有差異的電子振盪器,若在諧振電路中耦合,會以相同的頻率共振[3]。電子振盪器的自動同步是由爱德华·阿普尔顿在1923年發現的[4]。

1925年時,布里斯托尔大学電機系的大衛·羅賓森(David Robertson)教授,在威尔斯纪念大楼Great George鐘敲鐘出聲的時鐘控制電路中,引入了锁相的概念。羅賓森教授設計的鐘有一個機電裝置可以調整擺鐘的振動速率,所用的修正訊號是來自一個比較電路,在每天上午格林威治時間10點時,比較格林威治天文台的電報脈衝以及擺鐘的相位。其中除了現在電子鎖相迴路中會有的每一個組件之外,羅賓森的設計還有一個特點,其相位比較器是用繼電器邏輯的方式實現相位/頻率比較的機能,一直到1970年代之後才在電子電路中看到類似的設計。羅賓森的研究比後來1932年提出,後來命名為「锁相环」(phase-lock loop)的研究要早。1932年的研究是英國科學家設法想找到可以代替埃德温·霍华德·阿姆斯特朗的超外差收音机、同差檢測或直接變換接收機的方案。在同差系統中,會將本機振盪器調到想要的頻率,再乘上輸入的信號。所得的輸出信號會包括原始的調變資訊。原意是想發展一種調諧電路比超外差收音机要少的電路。因為本機振盪器的頻率會快速的飄移,會有自動修正信號加到振盪器上,使其頻率和相位和輸入信號相同。此技術是在1932年時,在Henri de Bellescize發表在法文期刊L'Onde Électrique的論文中所提及[5][6][7]。

至少從1930年代起,類比電視接收器的锁相环垂直掃描和水平掃描電路,都會和廣播信號的同步信號鎖相[8]。 西格尼蒂克在1969年推出了具有完整鎖相環機能的單片集成电路(例如NE565)[9],類似技術的應用就不斷的增加。後來RCA推出了CD4046互補式金屬氧化物半導體的微功率锁相环IC,是當時廣為使用的積體電路。

結構和功能

一个鎖相迴路电路通常由以下模块构成:

每个模块的简单原理描述如下:

- 鉴频鉴相器: 对输入的参考信号和反馈回路的信号进行频率和相位的比较,输出一个代表两者差异的信号至低通滤波器。

- 低通滤波器: 将输入信号中的高频成分滤除,保留直流部分送至压控振荡器。

- 压控振荡器: 输出一个周期信号,其频率由输入电压所控制。

- 反馈回路 : 将压控振荡器输出的信号送回至鉴频鉴相器。通常压控振荡器的输出信号的频率大于参考信号的频率,因此需在此加入分频器以降低频率。

分类

- 按照实现技术,可以分为模拟鎖相迴路(APLL,Analog PLL)和数字鎖相迴路(DPLL,Digital PLL)。

- 模拟鎖相迴路(Analog PLL)是指類比的鉴相器,濾波器可能是主動的,也可能是被動的。使用压控振荡器,若其迴路在原點恰有一個極點,則此APLL稱為type II鎖相迴路。

- 数字鎖相迴路(Digital PLL)是指數位的鉴相器,若濾波器、振盪器也都是數位的(如{{le|數控振盪器|Numerically-controlled oscillator|),則稱為全數位鎖相迴路(ADPLL,All digital PLL)

- 按照反馈回路,可以分为整数倍分频鎖相迴路(Integer-N PLL)和分数倍分频鎖相迴路(Fractional-N PLL)。

- 按照鉴频鉴相器的实现方式,可以分为电荷泵鎖相迴路(Charge-Pump PLL)和非电荷泵鎖相迴路。

- 按照环路的带宽,它可以分为宽带鎖相迴路(Wide band loop PLL)和窄带鎖相迴路(Narrow band loop PLL)。

性能指标

- 種類和階數

- 鎖相迴路範圍:hold-in範圍(追蹤範圍)、捕獲範圍、鎖定範圍[10]

- 稳定性指标:迴路頻寬,相位裕度(Phase margin)。

- 暫態響應:例如過沖、到特定精度(例如50 ppm)的安定時間。

- 穩態誤差:相位誤差或是時序誤差。

- 輸出頻譜純淨度:例如特定VCO調諧電壓漣波的邊帶。

- 相位雜訊:定義為特定頻帶的雜訊能量(例如載波上下10 kHz)。這和VCO相位雜訊、PLL頻寬高度相關。

- 通用參數:例如能耗、電源範圍、輸出振幅。

应用领域

鎖相環常用在同步應用中,例如太空同調解調和門限擴展(threshold extension)的通訊、位元同步和符號同步。鎖相環也用在频率调制信號的解調變。在無線電發射機中,會用PLL來合成新的頻率,是參考頻率的倍數,和參考頻率有相同的穩定度。

其他的應用有:

- 频率调制(FM)訊號的解調變:若PLL鎖定FM訊號,VCO會追蹤輸入信號的瞬時頻率。濾波後的誤差電壓會控制VCO,並且和輸入信號鎖定,這就是解調變後的FM輸出。VCO轉遞特徵會決定解調變輸出的線性度。因為用在PLL積分電路中的VCO是高度線性的信號,因此可以實現高線性度的FM解調變器。

- 頻率偏移調變(FSK)的解調變:用在數位資料通訊以及電腦週邊上,透過在二個事先設定頻率之間切換的信號來傳輸二進位資料。

- 小信號的恢复(用锁相放大器來追蹤參考頻率)

- 恢复資料流(例如來自碟盤存儲資料)的時脈資訊

- 微处理器的倍頻器,讓內部的處理器元件可以運行的比外部的時脈更快,而且有準確的比例關係。

- 调制解调器的解調變,以及电信和遙控訊號的音頻信號。

- 影響信號的数字信号处理。鎖相迴路也用來同步视频訊號的相位和頻率,因此可以取樣及進行數位處理。

- 非接觸式的原子力显微镜,偵測探針和表面的交叉作用產生的共振頻率。

- 直流电动机电机控制器

時脈恢復

有些資料流,特別是高速的串列資料流(例如硬碟磁頭讀到的原始資料流),在傳送時不會將其時脈信號一起送出。接收器利用類似的參考頻率來產生時脈,再利用PLL將其時脈和接收資料的相位鎖定同步。此程序稱為時脈恢復。為了時脈功能,資料流中必須有夠快的資料切換,以校正PLL振盪器的頻率飄移。一般而言,會使用一些线路码(例如8b/10b),讓二次資料切換時間間隔有一個明確的上限值。

偏移校正

若時脈和資料一起傳送,會用時脈為準來進行資料取樣。因為時脈接收後需放大,才能驅動正反器取樣資料。時脈邊緣和接收的資料窗之間會有一個有限大小的時間延遲,長度隨過程、溫度、電壓而不同。此時間延遲會限制傳送資料的速率。有一種消除延遲的方式是在接收端加入一個偏移校正(deskew)的PLL,使得每一次資料正反器的時脈都接收到的時間同相位。此應用中,常會使用一種特殊的锁相环,稱為Template:延遲鎖相環(DLL)[11]。

相關條目

- 頻率鎖定迴路

- 電荷泵鎖相迴路

- 載波恢復

- 科斯塔斯循環

- 延遲鎖定迴路(DLL)

- 直接變換接收機

- 直接数字合成

- 卡尔曼滤波

- 多位元鎖相迴路

- Shortt–Synchronome clock:相位鎖定主單擺的單擺(約1921年)

註解

- ^ 若頻率為常數,初始相位為零,弦波的相位就和時間成正比

參考資料

- ^ Christiaan Huygens, Horologium Oscillatorium … (Paris, France: F. Muguet, 1673), pages 18–19. From page 18: " … illudque accidit memoratu dignum, … brevi tempore reduceret." ( … and it is worth mentioning, since with two clocks constructed in this form and which we suspend in like manner, truly the cross beam is assigned two fulcrums [i.e., two pendulum clocks were suspended from the same wooden beam]; the motions of the pendulums thus share the opposite swings between the two [clocks], since the two clocks at no time move even a small distance, and the sound of both can be heard clearly together always: for if the innermost part [of one of the clocks] is disturbed with a little help, it will have been restored in a short time by the clocks themselves.) English translation provided by Ian Bruce's translation of Horologium Oscillatorium … , pages 16–17.

- ^ See:

- Lord Rayleigh, The Theory of Sound (London, England: Macmillan, 1896), vol. 2. The synchronization of organ pipes in opposed phase is mentioned in §322c, pages 221–222.

- Lord Rayleigh (1907) "Acoustical notes — VII," Philosophical Magazine, 6th series, 13 : 316–333. See "Tuning-forks with slight mutual influence," pages 322–323.

- ^ See:

- Vincent (1919) "On some experiments in which two neighbouring maintained oscillatory circuits affect a resonating circuit," Proceedings of the Physical Society of London, 32, pt. 2, 84–91.

- W. H. Eccles and J. H. Vincent, British Patent Specifications, 163 : 462 (17 Feb. 1920).

- ^ E. V. Appleton (1923) "The automatic synchronization of triode oscillators," Proceedings of the Cambridge Philosophical Society, 21 (Part III): 231–248. Available on-line at: Internet Archive.

- ^ Henri de Bellescize, "La réception synchrone," L'Onde Électrique (later: Revue de l'Electricité et de l'Electronique), vol. 11, pages 230–240 (June 1932).

- ^ See also: French patent no. 635,451 (filed: 6 October 1931; issued: 29 September 1932); and U.S. patent "Synchronizing system," no. 1,990,428 (filed: 29 September 1932; issued: 5 February 1935).

- ^ Notes for a University of Guelph course describing the PLL and early history, including an IC PLL tutorial 互联网档案馆的存檔,存档日期2009-02-24.

- ^ National Television Systems Committee Video Display Signal IO. Sxlist.com. [2010-10-14].

- ^ A. B. Grebene, H. R. Camenzind, "Phase Locking As A New Approach For Tuned Integrated Circuits", ISSCC Digest of Technical Papers, pp. 100–101, Feb. 1969.

- ^ Leonov, G. A.; Kuznetsov, N. V.; Yuldashev, M. V.; Yuldashev, R. V. Hold-in, pull-in, and lock-in ranges of PLL circuits: rigorous mathematical definitions and limitations of classical theory.. IEEE Transactions on Circuits and Systems I: Regular Papers (IEEE). 2015, 62 (10): 2454–2464. S2CID 12292968. arXiv:1505.04262

. doi:10.1109/TCSI.2015.2476295.

. doi:10.1109/TCSI.2015.2476295.

- ^ M Horowitz; C. Yang; S. Sidiropoulos. High-speed electrical signaling: overview and limitations (PDF). IEEE Micro. 1998-01-01. (原始内容 (PDF)存档于2006-02-21).

外部連結

- D.Banerjee, PLL Performance, Simulation and Design, Fourth Edition, Dog Ear Publishing, LLC, 2006.

- R.E. Best, Phase-Locked Loops: Design, Simulation, and Applications, McGraw-Hill Professional, 2003.

- F.M. Gardner, Phaselock Techniques, Wiley-Interscience, 2005.

- P.R. Gray et coll., Analysis and Design of Analog Integrated Circuits, Wiley, 2001.

- T.H. Lee, The Design of CMOS Radio-Frequency Integrated Circuits, Second Edition, Cambridge University Press, 2003.

- B. Razavi, RF Microelectronics, Prentice Hall, 1998.

- K. Shu et E. Sánchez-Sinencio, CMOS PLL Synthesizers: Analysis and Design, Springer, 2004.

- Predicting the Phase Noise and Jitter of PLL-Based Frequency Synthesizers (页面存档备份,存于互联网档案馆)

- MIT Open Course: 6.976 High Speed Communication Circuits and Systems, Spring 2003 (页面存档备份,存于互联网档案馆)

- William F. Egan, Phase-Lock Basics, Wiley-IEEE Press, 2 edition, November, 2007

- William F. Egan, Frequency Synthesis by Phase Lock, Wiley-Interscience, 2 edition December,1999

- Circuit sage: Phase Locked Loop Design (页面存档备份,存于互联网档案馆)

- Dennis Fischette's 1-Stop PLL Center (页面存档备份,存于互联网档案馆)

- Ask the Applications Engineer - 30 - PLL Synthesizers

- Jess Chen,“An introduction to the PLL library”, Cadence Design Systems document

- Agilent EEsof EDA Applications: Phase-Locked Loops (页面存档备份,存于互联网档案馆)

- PhD thesis: Modeling and simulation techniques for the accurate verification of Integer-N PLLs[永久失效連結]