锁相环

锁相回路(PLL: Phase-locked loops)是利用反馈(Feedback)控制原理实现的频率及相位的控制系统,其作用是将电路输出的信号与其外部的参考信号保持同步,当参考信号的频率或相位发生改变时,锁相回路会检测到这种变化,并且通过其内部的反馈系统来调节输出频率,直到两者重新同步,这种同步又称为“锁相”(Phase-locked)。

锁相回路有许多种,最简单的锁相回路会包括变频振荡器以及鉴相器,形成反馈回路。振荡器产生讯号,鉴相器比较输出讯号和输入周期讯号之间的相位,调整振荡器输出,设法和输入周期讯号同步。

若让输出讯号和输入讯号之间的相位一致,则两者的频率也会一致。因此,锁相回路除了让相位一致之外,也可以追踪输入讯号的频率,或是产生频率是输入讯号整数倍的信号。此特性可以用在电脑时脉的同步、解调变及频率合成。

锁相回路常用在无线电、电信、电子计算机及其他电子设备中。锁相回路也可以用来解调变讯号、从高噪声的通讯频道中恢复原始信号、产生频率为输入信号频率整数倍的频率(频率合成)、或在数字电路(例如微处理器)中产生准确的时钟脉冲。因为单一的集成电路即可提供完整的锁相回路机能,此技术已普遍使用在现在的电子设备中,输出频率从1Hz以下,到数GHz。

实际上类似的例子

赛车

锁相回路可以用赛车来说明:考虑两部车进行的绕圈赛车,一部车代表输入信号,另一部车代表锁相回路的输出,也就是压控振荡器(VCO)频率。每一圈代表一个完整的周期。每小时的圈数代表频率,两部车之间的距离代表信号之间的相位差。

大部分赛车的过程中,两部车都可以超过对方或落过对方,这类似锁相回路的非锁相状态。

但若有事故,赛车场会出现黄色警告旗,此时,任何一部车辆都不允许超过其他的车,也不允许被其他的车超过。此时的两部车就代表锁相回路在锁相状态下的输入信号和输出信号。每一个驾驶者都会量测其车辆和其他车辆的相位差。若和前车保持的距离太远了,会设法加速使距离拉近,若和前车保持的距离太近了,会设法减速使距离拉远。因此,两部车会保持固定的距离。因为车辆不允许超过其他的车,因此在相同时间内,两车绕的圈数会相同,因此两个信号的频率相同。

时钟的例子

相位和时间成正比[a],因此相位差可以用时间差来表示。时钟相对其他时钟而言,某程度上会有锁相(固定时间差),但准确度可能有些不同。

若让时钟自行运作,各时钟计时的速率会有些微的差距。例如墙上的钟每一小时可能会比国家标准技术研究所的钟快了几秒,随着时间过去,时间差会越来越大。

若要让墙上的钟和参考时钟同步,可能每一周会比较墙上的钟和参考时钟的时间(相位比较),然后调整墙上的钟。若没有调整,墙上的钟和参考时钟的偏差会越来越大。

有些时钟有计时调整功能,若比较时钟和标准时钟,发现时钟太快了,会设法让时钟的计时慢一点,若时钟太慢了,会设法让时钟的计时快一点。若顺利的话,时钟和标准时钟的误差会渐渐缩小。几周后,时钟就会准确的对应标准时钟(在时钟本身的稳定性范围内,频率和相位都和标准时钟一致)。

早期电动机械学中也有锁相回路,例如1921年的Shortt-Synchronome钟。

历史

丹麦物理学家克里斯蒂安·惠更斯早在1673年就发现弱耦合的摆钟会有自发性同步的情形[1]。在19世纪时,第三代瑞利男爵约翰·斯特拉特发现弱耦合的风琴管及音叉也有同步的情形[2]。1919年时,威廉·埃克尔斯和J. H. Vincent发现二个调谐到频率略有差异的电子振荡器,若在谐振电路中耦合,会以相同的频率共振[3]。电子振荡器的自动同步是由爱德华·阿普尔顿在1923年发现的[4]。

1925年时,布里斯托尔大学电机系的大卫·罗宾森(David Robertson)教授,在威尔斯纪念大楼Great George钟敲钟出声的时钟控制电路中,引入了锁相的概念。罗宾森教授设计的钟有一个机电装置可以调整摆钟的振动速率,所用的修正讯号是来自一个比较电路,在每天上午格林威治时间10点时,比较格林威治天文台的电报脉冲以及摆钟的相位。其中除了现在电子锁相回路中会有的每一个组件之外,罗宾森的设计还有一个特点,其相位比较器是用继电器逻辑的方式实现相位/频率比较的机能,一直到1970年代之后才在电子电路中看到类似的设计。罗宾森的研究比后来1932年提出,后来命名为“锁相回路”(phase-lock loop)的研究要早。1932年的研究是英国科学家设法想找到可以代替埃德温·霍华德·阿姆斯特朗的超外差收音机、同差检测或直接变换接收机的方案。在同差系统中,会将本机振荡器调到想要的频率,再乘上输入的信号。所得的输出信号会包括原始的调变资讯。原意是想发展一种调谐电路比超外差收音机要少的电路。因为本机振荡器的频率会快速的飘移,会有自动修正信号加到振荡器上,使其频率和相位和输入信号相同。此技术是在1932年时,在Henri de Bellescize发表在法文期刊L'Onde Électrique的论文中所提及[5][6][7]。

至少从1930年代起,模拟电视接收器的锁相回路垂直扫描和水平扫描电路,都会和广播信号的同步信号锁相[8]。 西格尼蒂克在1969年推出了具有完整锁相回路机能的单片集成电路(例如NE565)[9],类似技术的应用就不断的增加。后来RCA推出了CD4046互补式金属氧化物半导体的微功率锁相回路IC,是当时广为使用的集成电路。

结构和功能

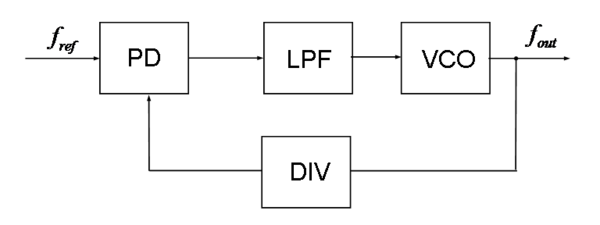

一个锁相回路电路通常由以下模块构成:

每个模块的简单原理描述如下:

- 鉴频鉴相器: 对输入的参考信号和反馈回路的信号进行频率和相位的比较,输出一个代表两者差异的信号至低通滤波器。

- 低通滤波器: 将输入信号中的高频成分滤除,保留直流部分送至压控振荡器。

- 压控振荡器: 输出一个周期信号,其频率由输入电压所控制。

- 反馈回路 : 将压控振荡器输出的信号送回至鉴频鉴相器。通常压控振荡器的输出信号的频率大于参考信号的频率,因此需在此加入分频器以降低频率。

分类

- 按照实现技术,可以分为模拟锁相回路(APLL,Analog PLL)和数字锁相回路(DPLL,Digital PLL)。

- 模拟锁相回路(Analog PLL)是指模拟的鉴相器,滤波器可能是主动的,也可能是被动的。使用压控振荡器,若其回路在原点恰有一个极点,则此APLL称为type II锁相回路。

- 数字锁相回路(Digital PLL)是指数字的鉴相器,若滤波器、振荡器也都是数字的(如数控振荡器),则称为全数字锁相回路(ADPLL,All digital PLL)

- 按照反馈回路,可以分为整数倍分频锁相回路(Integer-N PLL)和分数倍分频锁相回路(Fractional-N PLL)。

- 按照鉴频鉴相器的实现方式,可以分为电荷泵锁相回路(Charge-Pump PLL)和非电荷泵锁相回路。

- 按照环路的带宽,它可以分为宽带锁相回路(Wide band loop PLL)和窄带锁相回路(Narrow band loop PLL)。

性能指标

- 种类和阶数

- 锁相回路频率范围:hold-in范围(追踪范围)、捕获范围、锁定范围[10]

- 稳定性指标:回路带宽,相位裕度(Phase margin)。

- 暂态响应:例如过冲、到特定精度(例如50 ppm)的安定时间。

- 稳态误差:相位误差或是时序误差。

- 输出频谱纯净度:例如特定VCO调谐电压涟波的边带。

- 相位噪声:定义为特定频带的噪声能量(例如载波上下10 kHz)。这和VCO相位噪声、PLL带宽高度相关。

- 通用参数:例如能耗、电源范围、输出振幅。

减少抖动以及噪声

锁相回路的理想特性是是参考时脉和回授时脉的边缘可以对正。在PLL已经锁定时,两者相位的平均误差称为静态相位偏移(static phase offset)或稳态相位误差(steady-state phase error)。二个相位之间的变异称为追随抖动。理想上,静态相位偏移要是0,追随抖动越小越好[可疑]。

相位噪声是锁相回路会有的另一种抖动,是因为振荡器本身以及振荡器的频率控制电路元件所造成。在此一层面上,已有一些技术比其他技术的性能更好。最早的数字锁相回路是用射极耦合逻辑电路(ECL)组成,不过其功耗很高。若要让锁相回路有小的相位噪声,最好避免使用晶体管-晶体管逻辑(TTL)或的互补式金属氧化物半导体(CMOS)等饱和逻辑特性的零件[11]。

锁相回路的另一个理想特性是在电源及地的电压突然变化时,其产生的时脉频率和相位不会受到影响。这称为电源电压抑制比,抑制比越高越好。

若要改善输出的相位噪声,其VCO可以用注入锁定振荡器。

应用领域

锁相回路常用在同步应用中,例如太空同调解调和门限扩展(threshold extension)的通讯、位元同步和符号同步。锁相回路也用在频率调制信号的解调变。在无线电发射机中,会用PLL来合成新的频率,是参考频率的倍数,和参考频率有相同的稳定度。

其他的应用有:

- 频率调制(FM)讯号的解调变:若PLL锁定FM讯号,VCO会追踪输入信号的瞬时频率。滤波后的误差电压会控制VCO,并且和输入信号锁定,这就是解调变后的FM输出。VCO转递特征会决定解调变输出的线性度。因为用在PLL积分电路中的VCO是高度线性的信号,因此可以实现高线性度的FM解调变器。

- 频率偏移调变(FSK)的解调变:用在数字资料通讯以及电脑周边上,透过在二个事先设定频率之间切换的信号来传输二进制资料。

- 小信号的恢复(用锁相放大器来追踪参考频率)

- 恢复资料流(例如来自碟盘存储资料)的时脉资讯

- 微处理器的倍频器,让内部的处理器元件可以运行的比外部的时脉更快,而且有准确的比例关系。

- 调制解调器的解调变,以及电信和遥控讯号的音频信号。

- 影响信号的数码信号处理。锁相回路也用来同步视频讯号的相位和频率,因此可以取样及进行数字处理。

- 非接触式的原子力显微镜,侦测探针和表面的交叉作用产生的共振频率。

- 直流电动机电机控制器

时脉恢复

有些资料流,特别是高速的串列资料流(例如硬盘磁头读到的原始资料流),在传送时不会将其时脉信号一起送出。接收器利用类似的参考频率来产生时脉,再利用PLL将其时脉和接收资料的相位锁定同步。此程序称为时脉恢复。为了时脉功能,资料流中必须有够快的资料切换,以校正PLL振荡器的频率飘移。一般而言,会使用一些线路码(例如8b/10b),让二次资料切换时间间隔有一个明确的上限值 [12]。

偏移校正

若时脉和资料一起传送,会用时脉为准来进行资料取样。因为时脉接收后需放大,才能驱动正反器取样资料。时脉边缘和接收的资料窗之间会有一个有限大小的时间延迟,长度随过程、温度、电压而不同。此时间延迟会限制传送资料的速率。有一种消除延迟的方式是在接收端加入一个偏移校正(deskew)的PLL,使得每一次资料正反器的时脉都接收到的时间同相位。此应用中,常会使用一种特殊的锁相回路,称为延迟锁定回路(DLL)[13]。

展频

所有的电子系统都会发射一些不想要的无线电讯号。有许多的机构(例如美国的联邦通信委员会)会限制这些发射的能量,以及其带来的干扰。发射的噪声其频率一般会有一个尖锐的频谱峰值(一般是在元件的工作频率,或是其几倍的谐波)。系统设计者可以用展频(spread-spectrum)PLL,将频谱上的能量分散在其他频段,使峰值降低,以减少对高Q值接收器的干扰。例如,将工作频率略为往上或往下调整(约1%),工作在数百MHz的元件,可以将其干扰频谱扩展到数MHz的带宽范围内,这可以大幅减少对调频广播频道(其带宽是数万Hz)的干扰。

时脉分配

一般来说,芯片的参考时脉会驱动芯片中的锁相回路(PLL),接着驱动芯片内的时脉分配。时脉分配一般会以平衡分配,设法让时脉可以同时到达芯片的各个端点。其中一个端点是锁相回路的回授输入。锁相回路的功能是比较分配的时脉以及参考时脉,并且调整分配时脉的相位以及频率,使其分配时脉的相位以及频率和参考输入同步。

锁相回路无所不在,包括在距离数米的系统时钟校准,也用在芯片中的时脉里。有时参考信号不一定是单纯的时脉信号,也有可能是有够快资料转换的资料流,让锁相回路可以从资料流中取得正常且够快的时脉讯号。有时参考时脉的频率和分配时脉相同,也有可能分配时脉的频率和参考频率之间有有理数的比例关系。

AM侦测

锁相回路可以同步的解调变调幅(AM)信号。锁相回路会从调幅信号的载波中还原频率以及相位资料。VCO收到的相位会和载波差90度,因此会调整相位差使其同步,再送到乘法器中。乘法器的输出包括频率信号的和以及差,再经过低通滤波后取得解调变信号。因为PLL只会针对很接近VCO输出的载波频率有反应,因此PLL AM侦测器有高度的选择性以及噪声抑制能力,这是传统峰值型解调变器作不到的。不过,若调幅讯号的调变深度到100%,锁相回路可能会无法锁定(lose lock)[14]。

频率合成

在数字无线通讯系统(例如GSM、CDMA等)中,在传输时会用PLL针对本地振荡器进行上转换(up-conversion),在接收时也会对本地振荡器进行数字下转换。大部分的移动电话中,此一机能已整合到单一的集成电路中,以减小移动电话的成本及体积。在基地站,因为讯号需要的高性能,需要用分立元件来达到所需的性能。GSM本地振荡器模组一般会用频率合成器集成电路及分立的共振腔压控振荡器[来源请求]。

方块图

鉴相器会比较两个输入信号,并产生和其相位差成正比的误差信号,误差信号会经过低通滤波,之后驱动压控振荡器(VCO),以产生输出相位。此输出会透过回授回路(可能再加上除频器)再成为系统的回授输入,因此形成负反馈。若输出相位偏移,误差信号会增加,使压控振荡器的相位往另一个方向变化,以减少相位误差。因此输出相位可以锁定另一输入信号(称为参考信号)的相位[来源请求]。

模拟的锁相回路是由模拟的鉴相器、低通滤波器以及压控振荡器组成,形成负反馈的组态。数字的锁相回路则会有数字的鉴相器,也可能在参考信号、反馈路径(或两者都有)加上除频器,让PLL输出的频率可以维持为参考信号频率的有理数。若将反馈路径的除以N除频器改为可编程化的吞脉冲计数器,也可以让输出信号的频率是参考信号的非整数倍。

振荡器会产生周期性的输出信号。假设一开始振荡器的频率几乎和参考信号相同,若振荡器的相位落后参考信号,鉴相器会增加振荡器的控制电压,使其频率加快。若振荡器的相位领先参考信号,鉴相器会降低振荡器的控制电压,使其频率减慢。因为一开始振荡器的频率可能会和参考信号的频率差很多。实务上的鉴相器也会回应频率差,目的是增加可允许输入的锁定范围。依应用的不同,可能会用压控振荡器的输出作为PLL系统的输出,也可能是以给振荡器的控制信号作为系统输出[来源请求]。

组成

鉴相器

鉴相器(phase detector,简称PD)会产生对应二信号相位差的电压。在鉴相器中,鉴相器的信号输入分别是参考输入,以及压控振荡器(VCO)输出的回授信号。鉴相器的输出可以用来控制压控振荡器,使二信号之间的相位差可以调整为定值,因此整个系统是负回授系统 [15]。

不同种类的鉴相器有不同的性能特性。

例如,混频器会产生谐波,因此会产生不希望出现的频率边带,也称为参考突波(reference spurs),若希望压控振荡器(VCO)产生的是单一频率的讯号,这就会增加设计的复杂性。在滤波器设计需求中,会因为这部分的滤波而降低捕获范围,或是拉长锁定时间。在这些应用中会使用比较复杂的数字鉴相器,其输出不会有严重的参考突波问题。而且在锁波时,其输入的稳态的相差会接近90度[来源请求]。

在锁相回路应用中,常需要知道锁相回路是否有失锁(out of lock)的情形,比较复杂的数字鉴相器会有对应失锁的输出信号。

数字锁相回路中常会使用XOR 门当作简易鉴相器。若对线路作一些简单的修改,也可以用在模拟锁相回路中。

滤波器

锁相回路滤波器(多半是低通滤波器)一般会有两种不同的功能。

第一个功能是决定回路的动态特性(也称为稳定性)。这是指回路对扰动(例如参考频率的变动、田回授除频器的变化,或是启动)的响应特性。常见的考量是回路可以锁定的范围(pull-in范围、锁定范围、捕获范围),回路锁定的速度(lock时间,lock-up时间或安定时间)、阻尼特性等。依应用的不同,滤波器可能会是以下几种的一种或多种:单纯的比例(P,增益或衰减量)、积分(I,低通滤波器)、导数(D,高通滤波器)。回路的参数常会用波德图及相位裕度进行检验。控制理论中的常用概念(包括PID控制器)用设计此功能。

第二个功能是限制参考信号的频率能量范围(涟波),这是鉴相器输出以及VCO控制输入上的信号。此信号上若有不希望出现的频率边带,即为参考突波(reference spurs)。

此模组的设计可能主要会是上述二个功能中的一个,也有可能是比较复杂的模组,设法达到上述二功能。常见的取舍可能是增加系统带宽,但是会降低稳定值,或是加入阻尼使稳定性变好,但是降低系统反应速度,增加安定时间。上述的调整也会影响相位噪声。

振荡器

所有的锁相回路都会有可以调整输出频率的振荡器,可以是由模拟电路驱动的模拟振荡器(模拟锁相回路),或是像部分数字锁相回路(DPLL)的作法,使用数字模拟转换器(D-A converter)。若是全数字锁相回路(ADPLL),会用纯数字的振荡器[来源请求]。

回授路径以及除频器

可以在PLL的振荡器和回授输入之间加入除频器,以进行频率合成。在无线电发射器的应用中常会用到可编程的除频器,因为可以用稳定、准确但昂贵的单一频率石英晶体谐振器产生许多不同的频率。

有些PLL在参考时脉和给鉴相器的参考输入之间加入除频器。若回授回路有除的除频器,而参考输入有除的除频器,可以让PLL的频率为参考频率的倍。直接给锁相回路较低频率的参考输入似乎不难,不过有时参考频率因为其他因素而受到限制,因此会改在参考时脉和给鉴相器的参考输入之间加入除频器。

乘频率的PLL也可以用将电子振荡器的输出锁定在参考信号的N次谐波来实现。此时就不用单纯的鉴相器,会用谐波混合器(harmonic mixer)。谐波混合器会将参考信号变成有许多谐波的脉冲序列,[b]。VCO的输出会大约调整到接近其中的一个谐波。因此,想要的谐波混合器输出(表示N次谐波和VCO输出的差异)落在滤波器通带频率范围内。

回授回路中也不一定只能用除频器。回授回路中也可以用乘频器或频率混合器。乘频器会让VCO的输出是参考频率的几分之一。也可以是这些元件的组合。例如频率混合器加上除频器:这可以让除频器运作在很低的频率,但不会影响回路增益。

相关条目

- 频率锁定回路

- 电荷泵锁相回路

- 载波恢复

- 科斯塔斯循环

- 延迟锁定回路(DLL)

- 直接变换接收机

- 直接数字合成

- 卡尔曼滤波

- 多位元锁相回路

- Shortt–Synchronome clock:相位锁定主单摆的单摆(约1921年)

- 佛洛依德·加德纳:锁相回路研究的专家,有提出电荷泵锁相回路猜想(Gardner's conjecture on charge-pump phase-locked loops)及锁定范围问题(Gardner's problem on the lock-in range)

- 威廉·伊根,有提出对type II模拟锁相回路锁定范围的猜想(Egan's conjecture on the pull-in range of type II APLL)

注解

参考资料

- ^ Christiaan Huygens, Horologium Oscillatorium … (Paris, France: F. Muguet, 1673), pages 18–19. From page 18: " … illudque accidit memoratu dignum, … brevi tempore reduceret." ( … and it is worth mentioning, since with two clocks constructed in this form and which we suspend in like manner, truly the cross beam is assigned two fulcrums [i.e., two pendulum clocks were suspended from the same wooden beam]; the motions of the pendulums thus share the opposite swings between the two [clocks], since the two clocks at no time move even a small distance, and the sound of both can be heard clearly together always: for if the innermost part [of one of the clocks] is disturbed with a little help, it will have been restored in a short time by the clocks themselves.) English translation provided by Ian Bruce's translation of Horologium Oscillatorium … , pages 16–17.

- ^ See:

- Lord Rayleigh, The Theory of Sound (London, England: Macmillan, 1896), vol. 2. The synchronization of organ pipes in opposed phase is mentioned in §322c, pages 221–222.

- Lord Rayleigh (1907) "Acoustical notes — VII," Philosophical Magazine, 6th series, 13 : 316–333. See "Tuning-forks with slight mutual influence," pages 322–323.

- ^ See:

- Vincent (1919) "On some experiments in which two neighbouring maintained oscillatory circuits affect a resonating circuit," Proceedings of the Physical Society of London, 32, pt. 2, 84–91.

- W. H. Eccles and J. H. Vincent, British Patent Specifications, 163 : 462 (17 Feb. 1920).

- ^ E. V. Appleton (1923) "The automatic synchronization of triode oscillators," Proceedings of the Cambridge Philosophical Society, 21 (Part III): 231–248. Available on-line at: Internet Archive.

- ^ Henri de Bellescize, "La réception synchrone," L'Onde Électrique (later: Revue de l'Electricité et de l'Electronique), vol. 11, pages 230–240 (June 1932).

- ^ See also: French patent no. 635,451 (filed: 6 October 1931; issued: 29 September 1932); and U.S. patent "Synchronizing system," no. 1,990,428 (filed: 29 September 1932; issued: 5 February 1935).

- ^ Notes for a University of Guelph course describing the PLL and early history, including an IC PLL tutorial 互联网档案馆的存档,存档日期2009-02-24.

- ^ National Television Systems Committee Video Display Signal IO. Sxlist.com. [2010-10-14].

- ^ A. B. Grebene, H. R. Camenzind, "Phase Locking As A New Approach For Tuned Integrated Circuits", ISSCC Digest of Technical Papers, pp. 100–101, Feb. 1969.

- ^ Leonov, G. A.; Kuznetsov, N. V.; Yuldashev, M. V.; Yuldashev, R. V. Hold-in, pull-in, and lock-in ranges of PLL circuits: rigorous mathematical definitions and limitations of classical theory.. IEEE Transactions on Circuits and Systems I: Regular Papers (IEEE). 2015, 62 (10): 2454–2464. S2CID 12292968. arXiv:1505.04262

. doi:10.1109/TCSI.2015.2476295.

. doi:10.1109/TCSI.2015.2476295.

- ^ Basab Bijoy Purkayastha; Kandarpa Kumar Sarma. A Digital Phase Locked Loop based Signal and Symbol Recovery System for Wireless Channel. India: Springer (India) Pvt. Ltd. (Part of Springer Scinece+Business Media). 2015: 5. ISBN 978-81-322-2040-4.

- ^ M Horowitz; C. Yang; S. Sidiropoulos. High-speed electrical signaling: overview and limitations (PDF). IEEE Micro. 1998-01-01. (原始内容 (PDF)存档于2006-02-21).

- ^ M Horowitz; C. Yang; S. Sidiropoulos. High-speed electrical signaling: overview and limitations (PDF). IEEE Micro. 1998-01-01. (原始内容 (PDF)存档于2006-02-21).

- ^ Dixon, Robert, Radio Receiver Design, CRC Press: 215, 1998, ISBN 0824701615

- ^ Basab Bijoy Purkayastha; Kandarpa Kumar Sarma. A Digital Phase Locked Loop based Signal and Symbol Recovery System for Wireless Channel. India: Springer (India) Pvt. Ltd. (Part of Springer Scinece+Business Media). 2015: 94. ISBN 978-81-322-2040-4.

延伸阅读

- Banerjee, Dean, PLL Performance, Simulation and Design Handbook 4th, National Semiconductor, 2006 [2012-12-04], (原始内容存档于2012-09-02).

- Best, R. E., Phase-locked Loops: Design, Simulation and Applications, McGraw-Hill, 2003, ISBN 0-07-141201-8

- de Bellescize, Henri, La réception Synchrone, L'Onde Electrique, June 1932, 11: 230–240

- Dorf, Richard C., The Electrical Engineering Handbook, Boca Raton: CRC Press, 1993, Bibcode:1993eeh..book.....D, ISBN 0-8493-0185-8

- Egan, William F., Phase-Lock Basics, John Wiley & Sons, 1998. (provides useful Matlab scripts for simulation)

- Egan, William F., Frequency Synthesis by Phase Lock 2nd, John Wiley and Sons, 2000. (provides useful Matlab scripts for simulation)

- Gardner, Floyd M., Phaselock Techniques 3rd, Wiley-Interscience, 2005, ISBN 978-0-471-43063-6

- Klapper, J.; Frankle, J. T., Phase-Locked and Frequency-Feedback Systems, Academic Press, 1972. (FM Demodulation)

- Kundert, Ken, Predicting the Phase Noise and Jitter of PLL-Based Frequency Synthesizers (PDF) 4g, Designer's Guide Consulting, Inc., August 2006

- Liu, Mingliang, Build a 1.5-V 2.4-GHz CMOS PLL, Wireless Net Design Line, February 21, 2006, (原始内容存档于July 1, 2010). An article on designing a standard PLL IC for Bluetooth applications.

- Wolaver, Dan H., Phase-Locked Loop Circuit Design, Prentice Hall, 1991, ISBN 0-13-662743-9

外部链接

- D.Banerjee, PLL Performance, Simulation and Design, Fourth Edition, Dog Ear Publishing, LLC, 2006.

- P.R. Gray et coll., Analysis and Design of Analog Integrated Circuits, Wiley, 2001.

- T.H. Lee, The Design of CMOS Radio-Frequency Integrated Circuits, Second Edition, Cambridge University Press, 2003.

- B. Razavi, RF Microelectronics, Prentice Hall, 1998.

- K. Shu et E. Sánchez-Sinencio, CMOS PLL Synthesizers: Analysis and Design, Springer, 2004.

- Predicting the Phase Noise and Jitter of PLL-Based Frequency Synthesizers (页面存档备份,存于互联网档案馆)

- MIT Open Course: 6.976 High Speed Communication Circuits and Systems, Spring 2003 (页面存档备份,存于互联网档案馆)

- Circuit sage: Phase Locked Loop Design (页面存档备份,存于互联网档案馆)

- Dennis Fischette's 1-Stop PLL Center (页面存档备份,存于互联网档案馆)

- Ask the Applications Engineer - 30 - PLL Synthesizers

- Jess Chen,“An introduction to the PLL library”, Cadence Design Systems document

- Agilent EEsof EDA Applications: Phase-Locked Loops (页面存档备份,存于互联网档案馆)

- PhD thesis: Modeling and simulation techniques for the accurate verification of Integer-N PLLs[永久失效链接]