或门

| 基本逻辑閘 | |

| 緩衝 | 非 |

| 与 | 与非 |

| 或 | 或非 |

| 异或 | 同或 |

| 蘊含 | 蘊含非 |

| 输入 A B |

输出 A OR B | |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

或门(英語:OR gate)是数字逻辑中实现逻辑或的逻辑门,功能见右侧真值表。只要两个输入中至少有一个为高电平(1),则输出为高电平(1);若两个输入均为低电平(0),输出才为低电平(0)。换句话说,或门的功能是得到两个二进制数的最大值,而与门的功能是得到两个二进制数的最小值。

概述

[编辑]下列包括逻辑门的3种符号:形状特征型符号(ANSI/IEEE Std 91-1984)、IEC矩形国标符号(IEC 60617-12)和不再使用的DIN符号(DIN 40700)。其他的逻辑门符号见逻辑门符号表。

| 表达式 | 符号 | 功能表 | 继电器逻辑 | |||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ANSI/IEEE Std 91-1984 | IEC 60617-12 | DIN 40700 | ||||||||||||||||||

|

|

|

|

| ||||||||||||||||

2个输入以上的或门

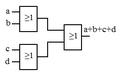

[编辑]输入个数最少的或门是2输入或门(OR2),但除此之外还有多个输入的与非门。确定或门需要的输入个数後,多输入或门就可用若干个2输入或门实现。下列图示展示了几种不同的设计方法,注意在设计时要注意信号的传播延迟问题以及需要的逻辑门数目,以选择最适宜的设计方案。

如果我们需要的输入个数小於多输入或门的输入个数,就要将不需要的输入接低电平(0,接地)。

-

OR4,由OR2实现,较为经济的方案

-

OR4,由OR2实现,不适宜的方案

-

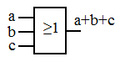

OR3减少输入实现的OR2

-

OR3

硬件描述和引脚分配

[编辑]

或门是基本的逻辑门,因此常用於TTL和CMOS集成电路逻辑系列。标准4000系列CMOS集成电路是4071,包含四个独立的2输入或门,而传统的TTL版本是7432。原始的7432或门有很多衍生版本的元件,这些元件都有相同的引脚分配,但内部结构是不同的,这使这些元件能在不同的电压范围以及更快的速度下进行运算。除标准2输入或门外,还有3输入和4输入或门。在CMOS系列中,型号有:

- 4075:三3输入或门

- 4072:双4输入或门

- 4071:四2输入或门

TTL变体包括:

- 74LS32:四2输入或门(小功率肖特基版本)

- 74HC32:四2输入或门 (高速CMOS版本) ,电流消耗低/电压范围大

- 74LVC32:上述芯片的低电压CMOS版本

硬件描述语言

[编辑]module(a,b,c); input a,b; output c; c = a or b; end module;

实现

[编辑] |

|

|

|

备选方案

[编辑]

如果没有专门的或门,可以用与非门实现或门,方法是将两个输入接在一起的与非门作为另外一个与非门的两个输入,即可实现或门。任何逻辑门都可以用与非门的组合实现。

线或

[编辑]在集电极开路门的逻辑输出为低电平有效时,或功能可以通过将数个输出接在一起来实现,这种布置称为“线或”,这时OC门的输出就如很多电路中的控制信号。或功能的实现尤其常用於仅为N或P型的晶体管集成电路的加工。